IPC-7351B CN_edit.pdf - 第55页

2 0 1 0 年 6 月 I P C - 7 3 5 I B CN 5 可 测 试 性 5 . 1 印 制 板 测 试 和 组 装 测 试 可 在 S M T 印 制 板 上 完 成 五 种 基 本 类 型 测 试 。 艮 P : a ) 检 查 未 组 装 元 器 件 印 制 板 短 路 和 开 路 的 裸 板 测 试 。 b ) 检 查 已 组 装 元 器 件 印 制 板 焊 接 短 路 的 制 造 缺 陷 分 析 。 c ) 每…

IPC-7351B CN

2010 年 6 月

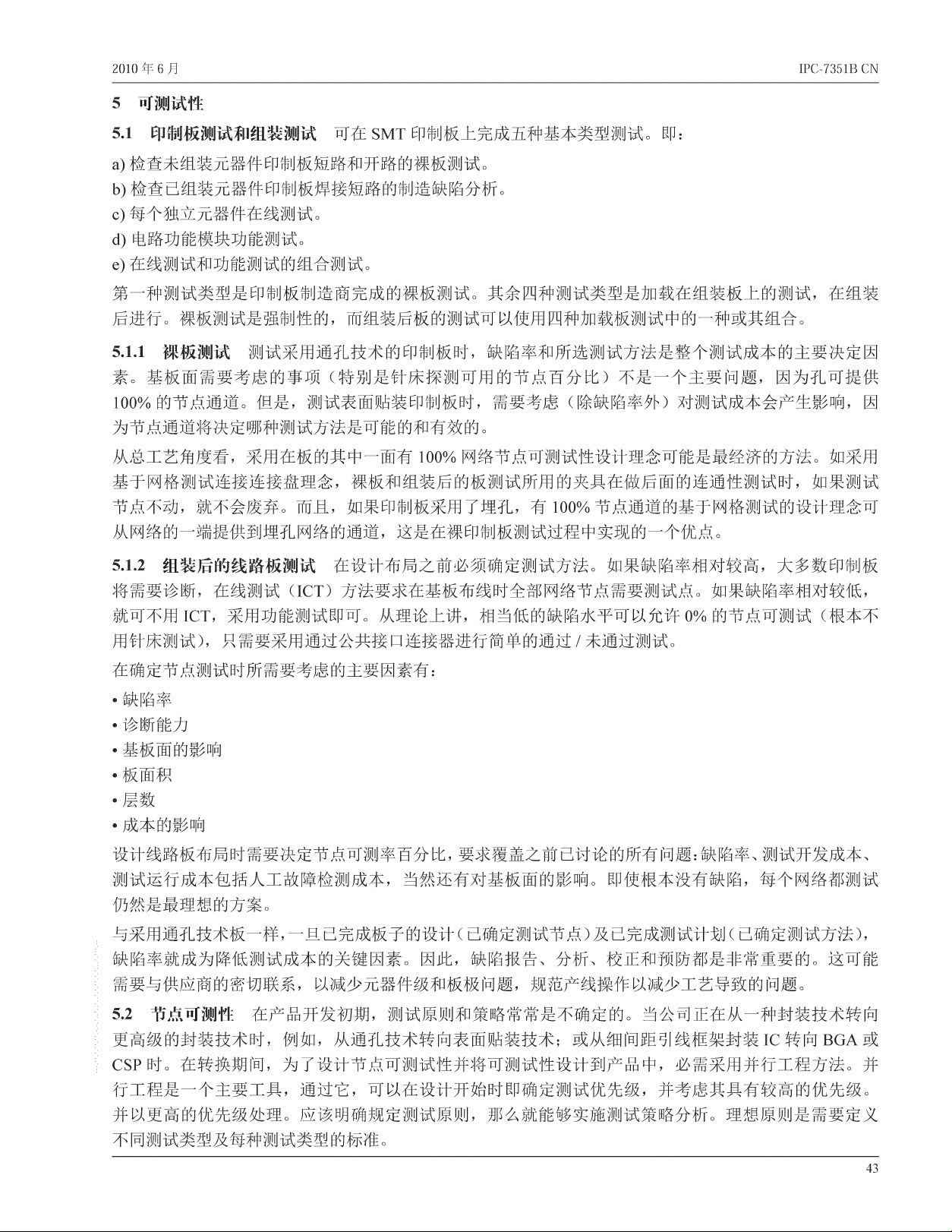

表 3 - 2 7 各种印制板表面涂层的主要属性

特征

HASL

OSP

化学 镀镍/浸

金

电解 镍/ 电

镀金 浸银 浸锡

保质期适当的处置

1 年

6 个月

大 于 1 年

小 于 1 年

6 个月 6 个月

与焊接表面的处置/接

触

应该避免

必须避免 应该避免 应该避免 必须避免 必须避免

SM T 连接盘表贴平整度

厚度不一致

平整 平整 平整 平整 平整

多 次 (4 ) 焊接

好

相当好,厚涂层

更好

相当好 相当好 相当好 相当好

免洗助焊剂的使用 没有问题

关 注 PTH/填充

孔

没有问题 没有问题 没有问题 没有问题

厚度 小于等 于1.0mm的

PC B 翘曲问题

有 无 无 无 无 无

焊点可靠性

好 好

B G A 黑盘和焊

点脆弱问题

金脆问题

好 好

板边缘接头

另外的电镀

操作

另外的电镀操作

另外的电镀操

作

另外的电镀

操作

另外的电镀

操作

另外的电镀

操作

打线邦定

无 无 无

是

无 无

测试点探针 好

差 ,除非在组装

期间施加焊料

好 好 好 好

组装后暴露的铜

无 是 无 无 无 无

开 关 /接头

无 无 是 是 是 无

P C B 制作中的废料处理

和安全性

差

好 一般 一般 好 好

表面涂层厚度控制

厚度控制问

题

好 好

金厚度控制

问题

好 好

总涂 层厚度|im*

2.0»8.0

最 小 0.15

[ 没有最大 ]

金 :0 .0 8 最小

[0.08^0.13]

镍 :3j0-6j0

金:0.13^0.75

11: 1.25-7,5

一 般 为 0.05

到

最 小 0.65

成本

1

1 ( 厚涂层)

12^1.5

1 1

* 在 1.6mm X L 6m m 的板厚连接盘上测出的厚度。

4 元器件质量验证

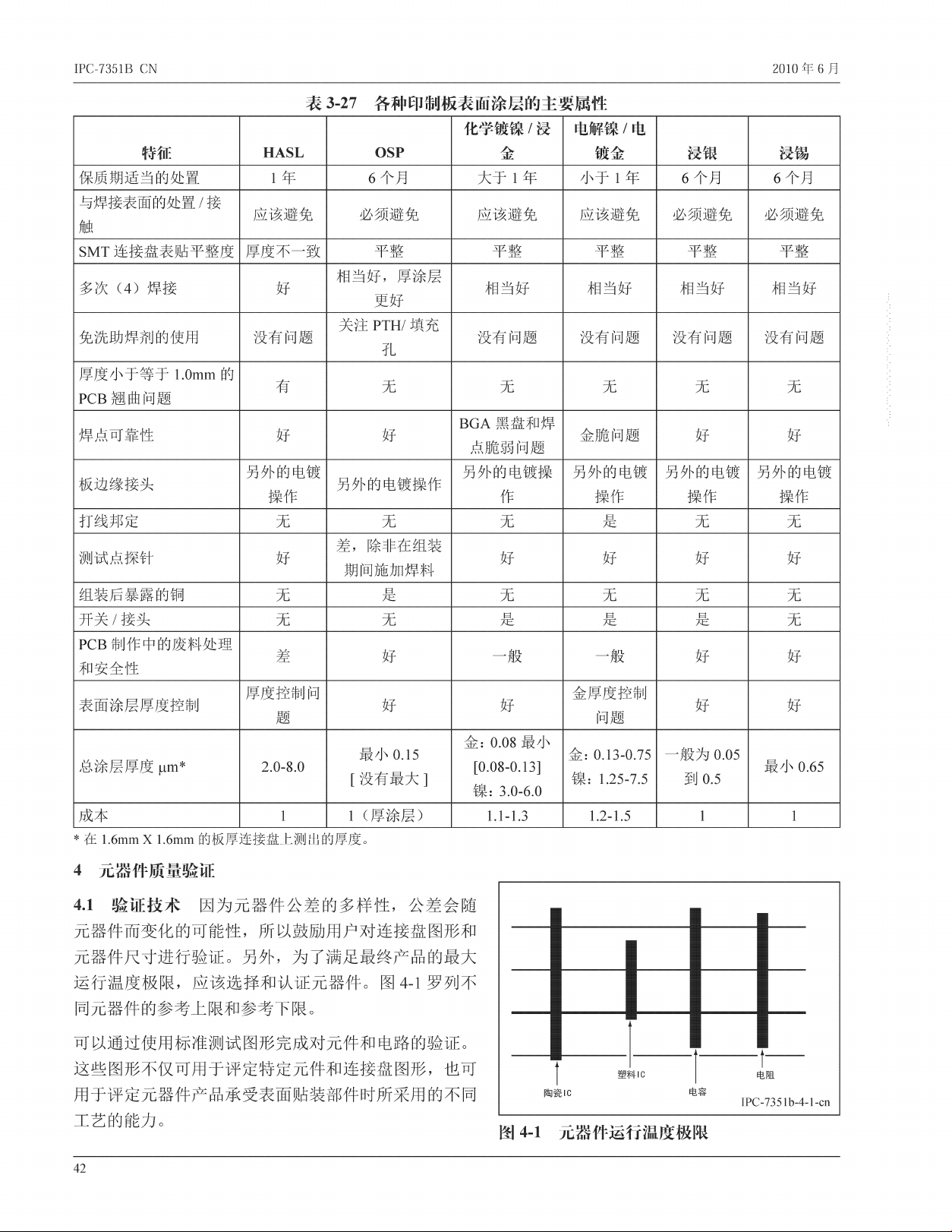

4 . 1 验 证 技 术 因 为 元 器 件 公 差 的 多 样 性 ,公差会随

元器件而变化的可能性,所以鼓励用户对连接盘图形和

元器件尺寸进行验证。另外,为了满足最终产品的最大

运行温度极限,应该选择和认证元器件。图 4 -1 罗列不

同元器件的参考上限和参考下限。

可以通过使用标准测试图形完成对元件和电路的验证。

这些图形不仅可用于评定特定元件和连接盘图形,也可

用于评定元器件产品承受表面贴装部件时所釆用的不同

工艺的能力。

图 4 - 1 元器件运行温度极限

42

201 0 年 6 月 IPC-735IB CN

5 可测试性

5 . 1 印 制 板 测 试 和 组 装 测 试 可 在 S M T 印制板上完成五种基本类型测试。艮P:

a ) 检查未组装元器件印制板短路和开路的裸板测试。

b ) 检查已组装元器件印制板焊接短路的制造缺陷分析。

c ) 每个独立元器件在线测试。

d ) 电路功能模块功能测试。

e ) 在线测试和功能测试的组合测试。

第一种测试类型是印制板制造商完成的裸板测试。其余四种测试类型是加载在组装板上的测试,在组装

后进行。裸板测试是强制性的,而组装后板的测试可以使用四种加载板测试中的一种或其组合。

5 . 1 . 1 裸 板 测 试 测 试 釆 用 通 孔 技 术 的 印 制 板 时 ,缺陷率和所选测试方法是整个测试成本的主要决定因

素 。基 板 面 需 要 考 虑 的 事 项 (特别是针 床探测可用的节点百 分比)不是一个主要问题,因为孔可提供

100% 的节点通道。但是,测试表面贴装印制板时,需 要 考 虑 (除缺陷率外)对测试成本会产生影响,因

为节点通道将决定哪种测试方法是可能的和有效的。

从总工艺角度看,釆用在板的其中一面有100% 网络节点可测试性设计理念可能是最经济的方法。如釆用

基于网格测试连接连接盘理念,裸板和组装后的板测试所用的夹具在做后面的连通性测试时,如果测试

节点不动,就不会废弃。而且,如果印制板釆用了埋孔,有 100% 节点通道的基于网格测试的设计理念可

从网络的一端提供到埋孔网络的通道,这是在裸印制板测试过程中实现的一个优点。

5 . 1 . 2 组装后的线 路板 测 试 在 设计 布 局 之 前必 须 确 定 测试 方法 。如果缺陷率相对较高,大多数印制板

将需要诊断,在 线 测 试 (I C T ) 方法要求在基板布线时全部网络节点需要测试点。如果缺陷率相对较低,

就可不用ICT,釆用功能测试即可。从理论上讲,相当低的缺陷水平可以允许0 % 的 节 点 可 测 试 (根本不

用针床测试) ,只需要釆用通过公共接口连接器进行简单的通过/ 未通过测试。

在确定节点测试时所需要考虑的主要因素有:

• 缺陷率

• 诊断能力

• 基板面的影响

• 板面积

•层数

• 成本的影响

设计线路板布局时需要决定节点可测率百分比,要求覆盖之前已讨论的所有问题: 缺陷率、测试开发成本、

测试运行成本包括人工故障检测成本,当然还有对基板面的影响。即使根本没有缺陷,每个网络都测试

仍然是最理想的方案。

与釆用通孔技术板一样,一旦已完成板子的设计(已确定测试节点)及已完成测试计划(已确定测试方法),

缺陷率就成为降低测试成本的关键因素。因此,缺陷报告、分析、校正和预防都是非常重要的。这可能

需要与供应商的密切联系,以减少元器件级和板极问题,规范产线操作以减少工艺导致的问题。

5 . 2 节 点 可 测 性 在 产 品 开 发 初 期 ,测试原则和策略常常是不确定的。当公司正在从一种封装技术转向

更高级的封装技术时,例如,从通孔技术转向表面贴装技术;或从细间距引线框架封装1C转 向 B G A 或

C S P 时。在转换期间,为了设计节点可测试性并将可测试性设计到产品中,必需釆用并行工程方法。并

行工程是一个主要工具,通过它,可以在设计开始时即确定测试优先级,并考虑其具有较高的优先级。

并以更高的优先级处理。应该明确规定测试原则,那么就能够实施测试策略分析。理想原则是需要定义

不同测试类型及每种测试类型的标准。

43

IPC-7351B CN

2010 年 6 月

5 . 2 . 1 测 试 原 则 应 该 制 定 测 试 原 则 ,使其涵盖产品所必须的测试方法的任意组合。然后 ,在开始设计

过程之前,确定实施所要求测试的简单策略。在产品开发周期的初期而不是结束时规划可测试性可明显

地降低每个节点的测试成本,并且可提高整个产品开发周期从最初的设计到最后的测试的可测试性。

最好的测试策略是为每种可釆用的测试方法做出规定。既使在开发周期的初期就很明确地规定了产品的

测试程序,在完成设计后,也可能会发生变化。概述测试原则时,需要考虑以下几点:

a) 所有元器件导通孔的布局策略

b) 提供每个网络测试节点

C ) 每个测试节点最好在印制板的相同面

d) 合适的测试点焊盘尺寸及间距

既使在高密度设计中,从板的任一面提供到每个网络节点的1.00%覆盖的原则也是能够实现的。但是在设

计开始时就必须做出这一决定。

5 . 2 . 2 裸 板 测 试 策 略 建 立 产 品 的 测 试 原 则 后 ,就可以定义测试策略或测试程序。纵观测试程序中的几

个要素,要考虑:

a ) 釆 用 A O I光学检测内层。

b ) 光学检测外层连接盘/ 导通孔连接。

c ) 裸板测试中,测试探针仅放置在任一面上的导通孔。

d ) 探针不能损伤SM T焊盘。

e ) 装载测试板后,探测可以放置在辅面的导通孔上。

f ) 将焊膏丝网印刷在密封板的导通孔上。

必须组织所有涉及测试的并行工程团队成员制定实际产品测试策略。这样将会确保各种测试类型及程序

的集合不会有太多的冗余或形成可能危及测试完整性的间隙。

5 . 3 组装板的所有节点可测试性测试板所需要的测试探针数等于装置节点的总数或装置之间公共连接

的总数。但 是 ,多数高密度表面贴装设计印制板,常常要求使用双面放置测试点或使用抓斗式测试夹具,

因为从板的一面不能测试所有的节点。

在线测 试 (In-Circuit Test,以下简称为ICT ) 只需要测试每个网络的任意节点。每个网络至少有两个节点,

有的有很多节点,例如:存储板上一个网络可能连接很多节点。为了 达 到 IC T 测试的全面覆盖,只测试

每个网络的任意一个节点即可。因此,完 成 IC T 所要求的

测试探针总数明显少于裸板测试所要求的数量。

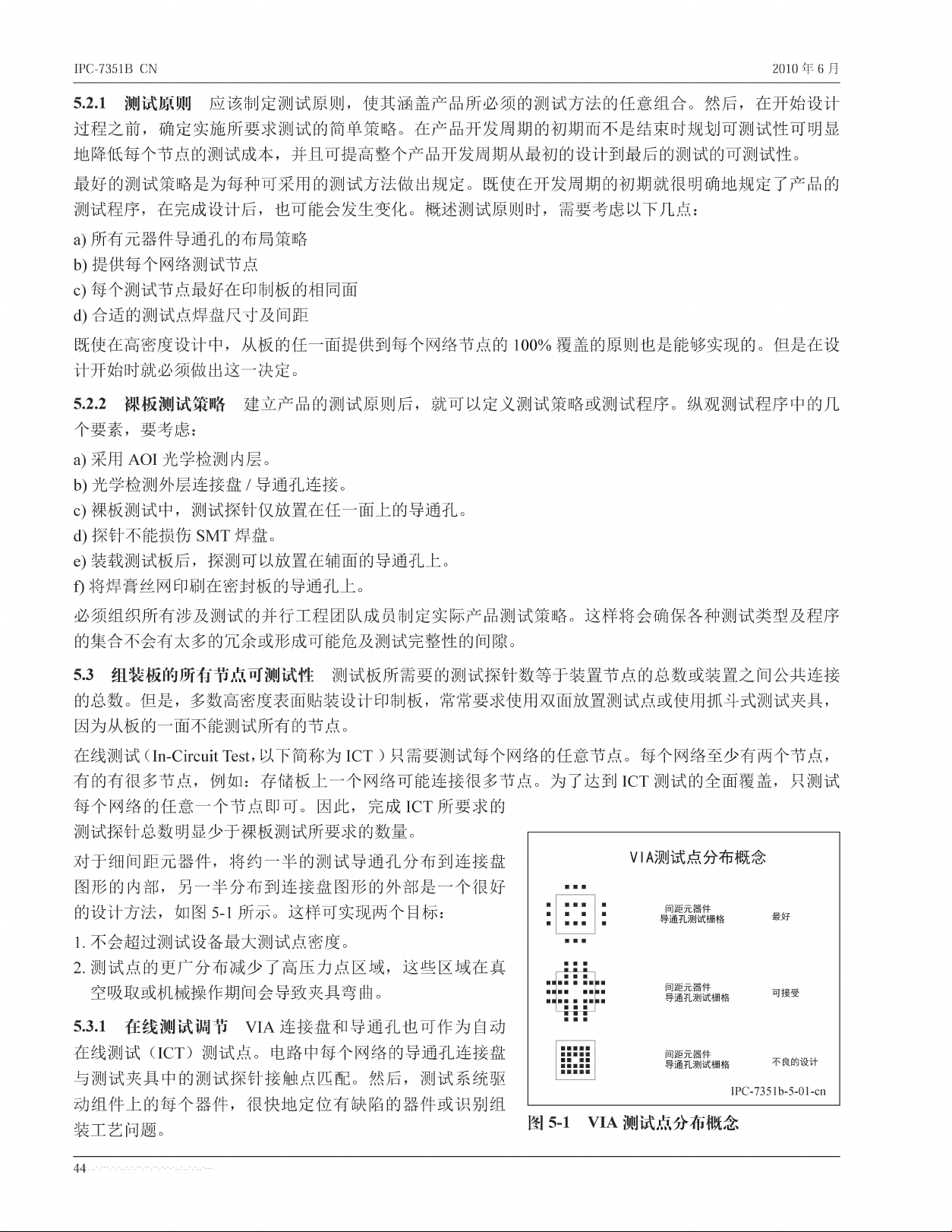

对于细间距元器件,将约一半的测试导通孔分布到连接盘

图形的内部,另一半分布到连接盘图形的外部是一个很好

的设计方法,如 图 5-1 所示。这样可实现两个目标:

L 不会超过测试设备最大测试点密度。

2 .测试点的更广分布减少了高压力点区域,这些区域在真

空吸取或机械操作期间会导致夹具弯曲。

5 . 3 . 1 在 线 测 试 调 节 V IA 连接盘和导通孔也可作为自动

在 线 测 试 (I C T ) 测试点。电路中每个网络的导通孔连接盘

与测试夹具中的测试探针接触点匹配。然 后 ,测试系统驱

动组件上的每个器件,很快地定位有缺陷的器件或识别组

装工艺问题。 图七1 V I A 测试点分布概念

VIA测试点分布概念

圖圔圖

圖 _ _ _

: 间距元器件 ^

圖

圖

圖 圖

圖圔圖

: 导通孔测试栅格 ®女子

圖圔圖

圖圖圖

■ ■ ■

圖圖圖

圖圖圖圖 圖圍

_圖 间距兀器件 與

„ 导通孔测试栅格

圖圖圖

圍圍圍

圖圖圖

间距元器件

圖圖 圖圖

导通孔测试栅格 不良的设1+

lPC~7351b~5~01~cn

44、