IPC-7351B CN_edit.pdf - 第44页

I P C - 7 35 1 B CN 2 0 1 0 年 6 月 a a m n n n n n n n n n o n n n n n n n 0 0 0 0 0 方 向 一 致 脚 标 识 统 一 间 距 J .P C ~ 7 3 5 1 b - 3 ~ 0 9 - c n 由 随 机 元 器 件 贴 装 产 生 的 两 个 影 响 是 在 所 有 层 ( 可 能 驱 动 层 数 ) 上 丢 失 统 一 的 基 于 网 格 的 测…

2010 年 6 月 IPC-7351BCN

易于出错的朝向

IPC-7351b-3-08-cn

首选朝向

焊桥

—

yyyyyyyy

n n n n n n n n

yyyy yyy y

nnn nnnn n

yyyyyyyy

nnnnnnnn

yyyy yyyy

nnnnnnnn

yyyy yyyy

波峰焊

图 3 - 8 波峰焊元器件排列朝向应用

3 . 4 . 1 . 3 元 器 件 的 贴 装 无论什么时候,元器件还应该组合在一起,通过网表或连通性及电路性能要求最

终决定元器件的贴装。相似类型的元器件应该以相同的朝向排成行,以简化元器件的贴装、检验及焊接。

例如,在存储板内,所有存储芯片都是放在一个明确指定的矩阵内,其中所 有 元 器 件 的 1 脚都朝向同一

个方向。

3 . 4 . 1 . 4 基 于 网 格 器 件 的 定 位 SM T 元器件在印制板上的贴装通常比通孔元器件的插装更复杂,原因有

两个:元器件的密度更高;需要双面贴装的能力;在高 密 度 的SM T 设计中,不同元器件连接盘之间的间

隔常常小于0.2mm。由 于 S M T元器件形状种类繁多,其基于网格布局不太实用。

3 . 4 设 计 规 则 本标准中推荐的印制电路板设计原理考虑了目前的测试和制造能力。超出这些能力的限

制要求工艺包括制造、工程及测试技术所有人员都要参与到设计中。在设计初期就为测试及制造考虑可

帮助高质量的产品快速投入生产中。

如元器件尚未列入本标准范围内,则应该咨询制造工程部门。

3 . 4 . 1 元器件间隔

3 . 4 . 1 . 1 元 器 件 需 考 虑 的 因 素 连接盘图形设计和元器件间隔会影响表面贴装组件的可靠性、可制造性、

可测试性及可维修性。要求封装与封装之间有最小的间隔以满足所有这些制造要求。封装与封装之间的

最大间隔受到了几个因素的限制,如可用的板面积、设备、重量需要考虑的事项及电路运行速度要求。

有些设计要求表面贴装元器件要尽可能的相互靠近。

3 . 4 . 1 . 2 波 峰 焊 元 器 件 的 排 列 朝 向 在需要波峰焊接其表面贴装元器件的任何印制板组件上,元器件相对

于波峰的朝向会导致过多的焊接工艺缺陷。如 图 3 - 8 的对比,优选的朝向可优化焊接工艺,当组件通过波

峰时可减少拖尾的或者被阴影遮盖住的接点上的焊桥。如果可能,应该使所有极性表面贴装元器件的放

置朝向相同。下面是其他一些适用条件:

a ) 所有无源元器件应该相互平行。

b) S OIC器件的长轴及无源元器件的长轴应该互相垂直

c ) 无源元器件的长轴应该与沿着波峰焊设备传送带的板传动方向垂直

is

li

(I

31

IPC-7351B CN

2010 年 6 月

a a m n n n n n n

n n n o n n n n n n n

00000

方向一致

脚标识 统一间距

J.PC~7351b-3~09-cn

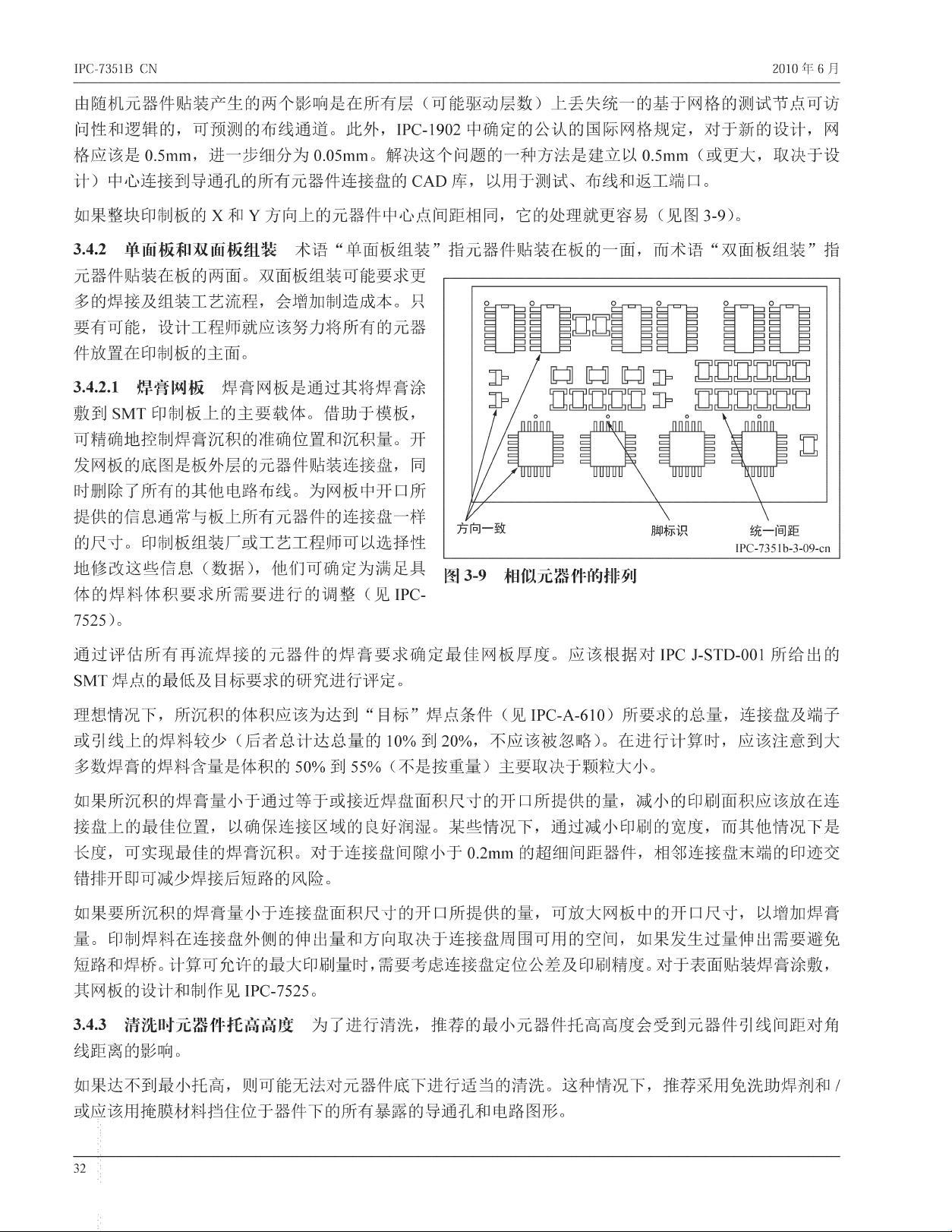

由随机元器件贴装产生的两个影响是在所有层(可能驱动层数)上丢失统一的基于网格的测试节点可访

问性和逻辑的,可预测的布线通道。此外 ,IPC -1902中确定的公认的国际网格规定,对于新的设计,网

格应该 是0.5mm,进一步细分为0.05mm。解决这个问题的一种方法是建立以0.5mm ( 或更大,取决于设

计 )中心连接到导通孔的所有元器件连接盘的C A D 库 ,以用于测试、布线和返工端口。

如果整块印制板的X 和 Y 方向上的元器件中心点间距相同,它的处理 就 更容易 (见 图 3-9)。

3 . 4 . 2 单 面 板 和 双 面 板 组 装 术 语 “ 单面板组装” 指元器件贴装在板的一面,而 术 语 “ 双面板组装”指

元器件贴装在板的两面。双面板组装可能要求更

多的焊接及组装工艺流程,会增加制造成本。只

要有可能,设计工程师就应该努力将所有的元器

件放置在印制板的主面。

3.4.2.1 f i 焊膏网板是通过其将焊膏涂

敷 到 S M T 印制板上的主要载体。借助于模板,

可精确地控制焊膏沉积的准确位置和沉积量。开

发网板的底图是板外层的元器件贴装连接盘,同

时删除了所有的其他电路布线。为网板中开口所

提供的信息通常与板上所有元器件的连接盘一样

的尺寸。印制板组装厂或工艺工程师可以选择性

地修改这些{目 息 ( 数 据 ),他们可确定为满足具 图 3-9 | 目似元器件的歹!J

体 的 焊 料 体 积 要 求 所 需 要 进 行 的 调 整 (见 IPC- 、

7525)。

通过评 估 所 有再流 焊 接 的 元器件的焊膏要求确定最佳网板厚度。应 该 根 据 对 IPC J-STD-001所给出的

SM T焊点的最低及目标要求的研宄进行评定。

理想情况下,所沉积的体积应该为达到“ 目标” 焊 点 条 件 (见 IP C -A -6 10)所要求的总量,连接盘及端子

或引 线 上 的 焊 料 较 少 (后 者 总 计达总量 的 10% 到 20%,不应该被忽略)。在进行计算时,应该注意到大

多数焊膏的焊料含量是体积的5 0% 到 55% ( 不是按重量)主要取决于颗粒大小。

如果所沉积的焊膏量小于通过等于或接近焊盘面积尺寸的开口所提供的量,减小的印刷面积应该放在连

接盘上的最佳位置,以确保连接区域的良好润湿。某些情况下,通过减小印刷的宽度,而其他情况下是

长度,可实现最佳的焊膏沉积。对于连接盘间隙小于0.2m m 的超细间距器件,相邻连接盘末端的印迹交

错排开即可减少焊接后短路的风险。

如果要所沉积的焊膏量小于连接盘面积尺寸的开口所提供的量,可放大网板中的开口尺寸,以增加焊膏

量 。印制焊料在连接盘外侧的伸出量和方向取决于连接盘周围可用的空间,如果发生过量伸出需要避免

短路和焊桥。计算可允许的最大印刷量时,需要考虑连接盘定位公差及印刷精度。对于表面贴装焊膏涂敷,

其网板的设计和制作见IPC-7525。

3 . 4 . 3 清 洗 时 元 器 件 托 高 高 度 为 了 进 行 清 洗 ,推荐的最小元器件托高高度会受到元器件引线间距对角

线距离的影响。

如果达不到最小托高,则可能无法对元器件底下进行适当的清洗。这种情况下,推荐釆用免洗助焊剂和/

或应该用掩膜材料挡住位于器件下的所有暴露的导通孔和电路图形。

II

on

H

on

n

l.

i n n

^

_

o i l

n

n

SB

r

_ D

is

on

32

2010 年 6 月 IPC-7351BCN

OOOOOOOOOOiffi 齋

■ 0 0 0 0 0 0 0 0 0 0

每 个 超 细 间 距元 件器 件 的

基 准 点 最 好 在 其 对 角 上 。

IPC-7351b-3-ll-cn

图 3 - 1 1 局部基准

——

.......................

—

............

… 33

3 . 4 . 4 基 准 标 记 基准标记是印刷的底图要素,它形成于与电路底图相同的制作工艺,用于光学识别系

统 。必须在同一个工序中蚀刻出基准标记和电路图形底图。

基准标记为组装工艺的所有工序提供了共同的基准点。这样就使得组装所用的每一个设备精确地定位电

路图形。有两种类型的基准标记。

3 . 4 .4 . 1 拼 板 和 整 板 基 准 整板基准标记用于定位单个板上的所有电路要素的位置。以拼板形式处理多个

图像电路时,整板基准就作为拼板基准(见 图 3-10)。

为了 校 正 偏 移 (X位置和y 位置)、旋 转 偏 移 (e 位置)及非线性 失真(缩放、拉伸和扭曲),要求至少要有三

个基准标记,且在电路或在拼板上以正交方式尽可能远离。

如 图 3 -12所示的基于三点网格的数据系统中定位整板或

拼板基准是一种很好的设计实践。第一个基准点在原点

0 -0 位 置 ,第二 个 及 第 三 个 基 准 点 为 正 象 限 中 从 0 到 0

的 X和 y 方向。对于表面贴装和通孔元器件制程,主面

和辅面应该都要有整板基准点。因为即便是通孔组装也

开始使用可视化对准系统。

3 . 4 . 4 . 2 局 部 基 准 局部基准标记用于定位要求更精密

贴装的单个元器件。

对于这些元器件,需要两个局部基准标记来校正平移偏

移 (x 和 y 位置)和 旋 转 偏 移 (0 位置)。这可以是位于连

接盘图形内或外围的对角线上的两个标记(参见图3-11)。

所有细间距元器件都应该具有两个局部基准标记,设计

成元件元器件图案,以确保在将元器件放置、移除和/ 或更换到印制板上时有足够的基准可用。所有的基

准应该有一个足够大阻焊膜开口,以保证基准标记上绝对没有阻焊膜。如果阻焊膜到达光学点上,一些

视觉对准系统可能会因为目标位置的对比度不足而受影响。

如果空间有限,两个相邻的元器件可以共享一个基准(见 图 3-12)。同样,如空间有限且印制线路板尺寸

很小,元器件的基准标记可以省略并使用整板基准来代替。

拼板基准

彳整板基准

IPC-7351b-3-10-cn

图 3 - 1 0 整 板 /拼板基准

<

-----

^

j >

<

-----

^

c

-----

)

<

-----

)

<. >

<

-----

^

c

-----

)

<

-----

)

圍