MIL- STD-883F 2004 TEST METHOD STANDARD MICROCIRCUITS.pdf - 第629页

MIL-STD-883F METHOD 5005.14 18 June 2004 13 TABLE V. Group E ( radiati on hardness ass urance t ests ) . 1/ Test MIL- STD-883 Class le vel S Class le vel B Method Conditi on Quantit y/ accept number Notes Quantit y/ acce…

MIL-STD-883F

METHOD 5005.14

18 June 2004

12

TABLE IV. Group D (package related tests) (for class levels B and S) - Continued.

3

/ The sample size number of 45, C = 0 for lead integrity shall be based on the number of leads or terminals tested

and shall be taken from a minimum of 3 devices. All devices required for the lead integrity test shall pass the seal

test if applicable (see 4

/) in order to meet the requirements of subgroup 2. For leaded chip carrier packages, use

condition B1. For pin grid array leads and rigid leads, use method 2028. For leadless chip carrier packages only,

use test condition D and a sample size number of 15 (C = 0) based on the number of pads tested taken from 3

devices minimum.

4

/ Seal test (subgroup 2b) need be performed only on packages having leads exiting through a glass seal.

5

/ Devices used in subgroup 3, "Thermal and Moisture Resistance" may be used in subgroup 4, "Mechanical".

6

/ Lead bend stress initial conditioning is not required for leadless chip carrier packages. For fine pitch packages

(≤ 25 mil pitch) using a nonconductive tie bar, preconditioning shall be required on 3 devices only prior to the

moisture resistance test with no subsequent electrical test required on these 3 devices. The remaining 12 devices

from the sample of 15 devices do not require preconditioning but shall be subjected to the required endpoint

electrical tests.

7

/ After completion of the required visual examinations and prior to submittal to method 1014 seal tests, the devices

may have the corrosion by-products removed by using a bristle brush.

8

/ At the manufacturer's option, end-point electrical parameters may be performed after moisture resistance and

prior to seal test.

9

/ Visual examination shall be in accordance with method 1010 or 1011.

10

/ Test three devices; if one fails, test two additional devices with no failures. At the manufacturer's option, if the

initial test sample (i.e., 3 or 5 devices) fails a second complete sample may be tested at an alternate laboratory

that has been issued suitability by the qualifying activity. If this sample passes the lot shall be accepted provided

the devices and data from both submissions is submitted to the qualifying activity along with 5 additional devices

from the same lot. If sample size (accept number) of 5(1) is used to pass the lot, the manufacturer shall evaluate

his product to determine the reason for the failure and whether the lot is at risk.

11

/ The adhesion of lead finish test shall not apply for leadless chip carrier packages.

12

/ Sample size number based on number of leads.

13

/ Lid torque test shall apply only to packages which use a glass-frit-seal to lead frame, lead or package body (i.e.,

wherever frit seal establishes hermeticity or package integrity).

MIL-STD-883F

METHOD 5005.14

18 June 2004

13

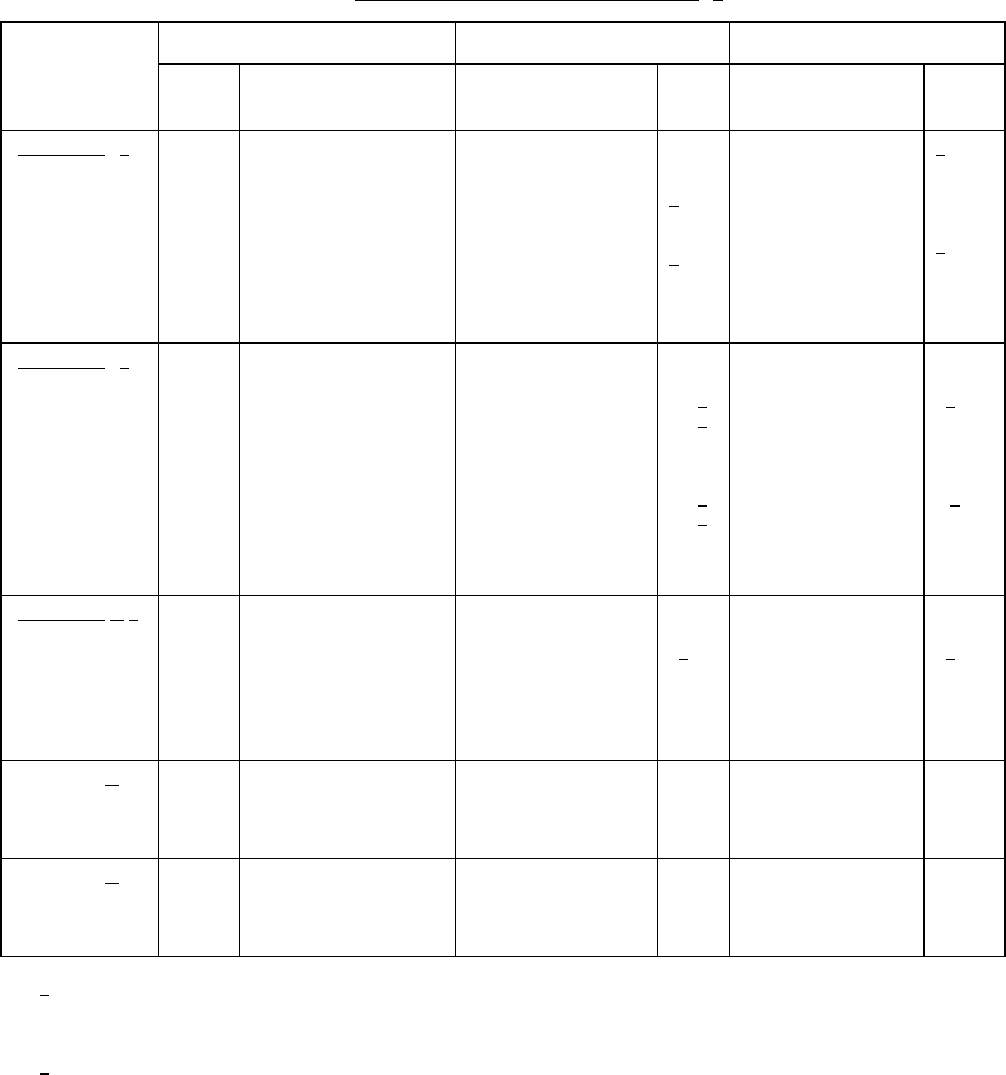

TABLE V. Group E (radiation hardness assurance tests). 1/

Test

MIL-STD-883 Class level S Class level B

Method

Condition

Quantity/

accept

number

Notes

Quantity/

accept

number

Notes

Subgroup 1 2/

Neutron

irradiation

a. Qualification

b. QCI

Endpoint

electrical

parameters

1017

25°C

As specified in

accordance with

device specification

(a) 2(0) devices/wafer

11(0) devices/wafer lot

(b) 2(0) devices/wafer

11(0) devices/wafer lot

3

/

3

/

(a) 2(0) device/wafer

5(0) devices/wafer lot

11(0) devices/

inspection lot

(b) 2(0) devices/wafer

5(0) devices/wafer lot

11(0) devices/

inspection lot

4/

4

/

Subgroup 2 5/

Steady-state

total dose

irradiation

a. Qualification

b. QCI

Endpoint

electrical

parameters

1019

25°C

Maximum supply voltage

As specified in

accordance with

device specification

(a) 4(0) devices/wafer

2(0) devices/ wafer

22(0) devices/wafer lot

(b) 4(0) devices/wafer

2(0) devices/wafer

22(0) devices/wafer lot

(a) 6

/

8

/

(b) 6

/

8

/

(a) 2(0) devices/wafer

5(0) devices/wafer lot

22(0) devices/

inspection

(b) 2(0) devices/wafer

5(0) devices/wafer lot

22(0) devices/

inspection lot

7

/

7

/

Subgroup 3 2/ 9/

Transient

ionizing

irradiation

Endpoint

electrical

parameters

1021

Digital

1023

Linear

25°C

As specified in

accordance with

device specification

2(0) devices/wafer

11(0)

devices/wafer lot

3

/

2(0) devices/wafer

11(0)

devices/

inspection lot

4

/

Subgroup 4 2/

Radiation latch-

up

1020

As specified in the device

specification

As specified in the

device specification

As specified in the

device specification

Subgroup 5 2/

Single event

effects

ASTM

F-1192

As specified in the device

specification

4(0) deviceswafer

1

/ Parts used for one subgroup test may not be used for other subgroups but may be used for higher levels in the same

subgroup. Total exposure shall not be considered cumulative unless testing is performed within the time limits of the

test method. Group E tests may be performed prior to device screening (see 3.5.3).

2/ This test is to be conducted only when specified in the purchase order or contract.

3

/ In accordance with wafer lot. If one part fails, seven additional parts may be added to the test sample with no

additional failures allowed, 18(1).

MIL-STD-883F

METHOD 5005.14

18 June 2004

14

TABLE V. Group E (radiation hardness assurance tests) - Continued. 1/

4

/ In accordance with inspection lot. If one part fails, seven additional parts may be added to the test sample with no

additional failures allowed, 18(1).

5

/ Class level B devices shall be inspected using either the class level B quantity/accept number criteria as specified, or

by using the class level S criteria on each wafer.

6

/ In accordance with wafer for device types with less than or equal to 4,000 equivalent transistors/chip selected from

the wafer. The manufacturer shall define and document sampling procedures.

7

/ In accordance with inspection lot. If one part fails, 16 additional parts may be added to the test sample with no

additional failures allowed, 38(1).

8

/ In accordance with wafer for device types with greater than 4,000 equivalent transistors/chip selected from the wafer.

The manufacturer shall define and document sampling procedures.

9

/ Upset testing during qualification on first QCI shall be conducted when specified in purchase order or contract. When

specified, the same microcircuits may be tested in more than one subgroup.

3.5.2 Alternate group B inspection for class level B

. At the manufacturer's option, (class level B only), group B inspection

shall be performed on any inspection lot of each qualified package type and lead finish from each different week of sealing.

Different inspection lots may be used for each subgroup. After this alternate group B inspection is successfully completed,

all other device types manufactured on the same assembly line using the same package type and lead finish sealed in the

same week may be accepted without further group B testing. A manufacturer shall not accept inspection lots containing

devices of a particular package type and lead finish until after the successful completion of group B testing for that package

type and lead finish for each week of seal.

3.5.2.1 Nonconformance for the alternate group B inspection

. When a failure has occurred in group B using the alternate

group B procedure, samples from three additional inspection lots of the same package type, lead finish, and week of seal as

the failed package shall be tested to the failed subgroup(s). If all three inspection lots pass, then all devices manufactured

on the same assembly line using the same package type and lead finish and sealed in the same week may be accepted for

group B inspection. If one or more of the three additional inspection lot fail, then no inspection lot containing devices

manufactured on the same assembly line using the same package type and lead finish sealed in the same week shall be

accepted for group B inspection until each inspection lot has been subjected to and passed the failed subgroup(s).

3.5.3 Group E samples

. At the manufacturer's option (but subject to the criteria defined by 3.5.3.1, 3.5.3.2, and 3.5.3.3),

group E samples need not be subjected to all the screening tests of method 5004, but shall be assembled in a group D

qualified package and, as a minimum, pass group A, subgroups 1 and 7, electrical tests at 25°C prior to irradiation.

3.5.3.1 Group E tests shall be performed on samples that have been exposed to burn-in or

3.5.3.2 as an alternative, the requirement of 3.5.3.1 can be waived if previous testing has shown that burn-in produces

negligible changes in the device total dose response or

3.5.3.3 as an alternative, the Group E tests can be performed on samples which have not received burn-in if the results of

the Group E tests are corrected for the changes in total dose response which would have been caused by burn-in. This

correction shall be carried out in a manner acceptable to the parties to the test.

3.6 Disposition of samples

. Disposition of sample devices used in groups A, B, C, D, and E testing shall be in

accordance with the applicable device specification.

3.7 Substitution of test methods and sequence

.

3.7.1 Accelerated qualification or quality conformance testing for class level B

. When the accelerated temperature/time

test conditions of condition F of method 1005 are used for any operating life or steady state reverse bias subgroups on a

given sample for purposes of qualification or quality conformance inspection, the accelerated temperature/time test

conditions shall be used for all of those named subgroups. When these accelerated test conditions are used for burn-in

screening test (test condition F of method 1015) or stabilization bake (any test temperature above the specified maximum

rated junction temperature for devices with aluminum/ gold metallurgical systems) for any inspection lot, it shall be

mandatory that they also be used for the operating life, and steady-state reverse bias tests of method 5005, as applicable, or

qualification or quality conformance inspection. Qualification and quality conformance inspection may be performed using

accelerated conditions on inspection lots that have been screened using normal test conditions.