S1.pdf - 第18页

Slide 18 Resist improved more than 2x in the last 6 years Improved Line Width Roughn ess (L WR) and dose as measured by Z-factor* EUVJ-2107 2013 2014 2015 2016 2017 2018 2019 Dose 50mJ 58mJ 42mJ 23mJ 21mJ 38 mJ 37mJ L W …

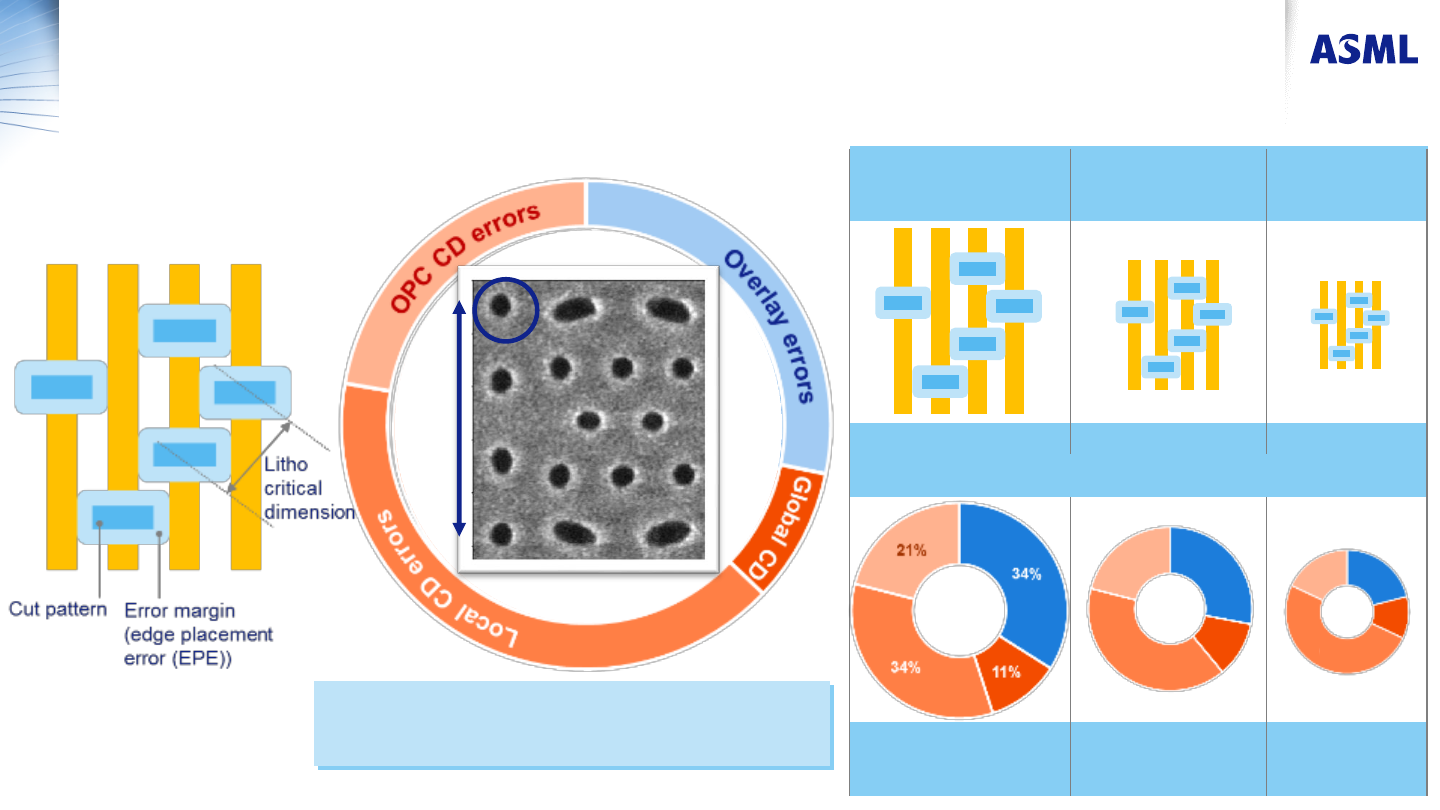

Scaling drives multiple patterning performance

Driven by Edge Placement Error and increasing local CD and placement

7nm 5nm

3nm

15 ~ 20nm

Typical Logic Pattern

Typical Logic EPE budget

9 ~ 13nm

12 ~ 14nm 8 ~ 11nm

7 ~ 9nm 5 ~ 7nm

50%

21%

12%

18%

EPE budget

Logic Node

CD: Critical Dimension, OPC: Mask Optical Proximity Correction

Minimum Half Pitch

40%

28%

11%

21%

Edge placement error (EPE): combined error

of overlay and CD uniformity (global CDU,

local stochastic and OPC error)

250 nm

Slide 17

Public

Slide 18

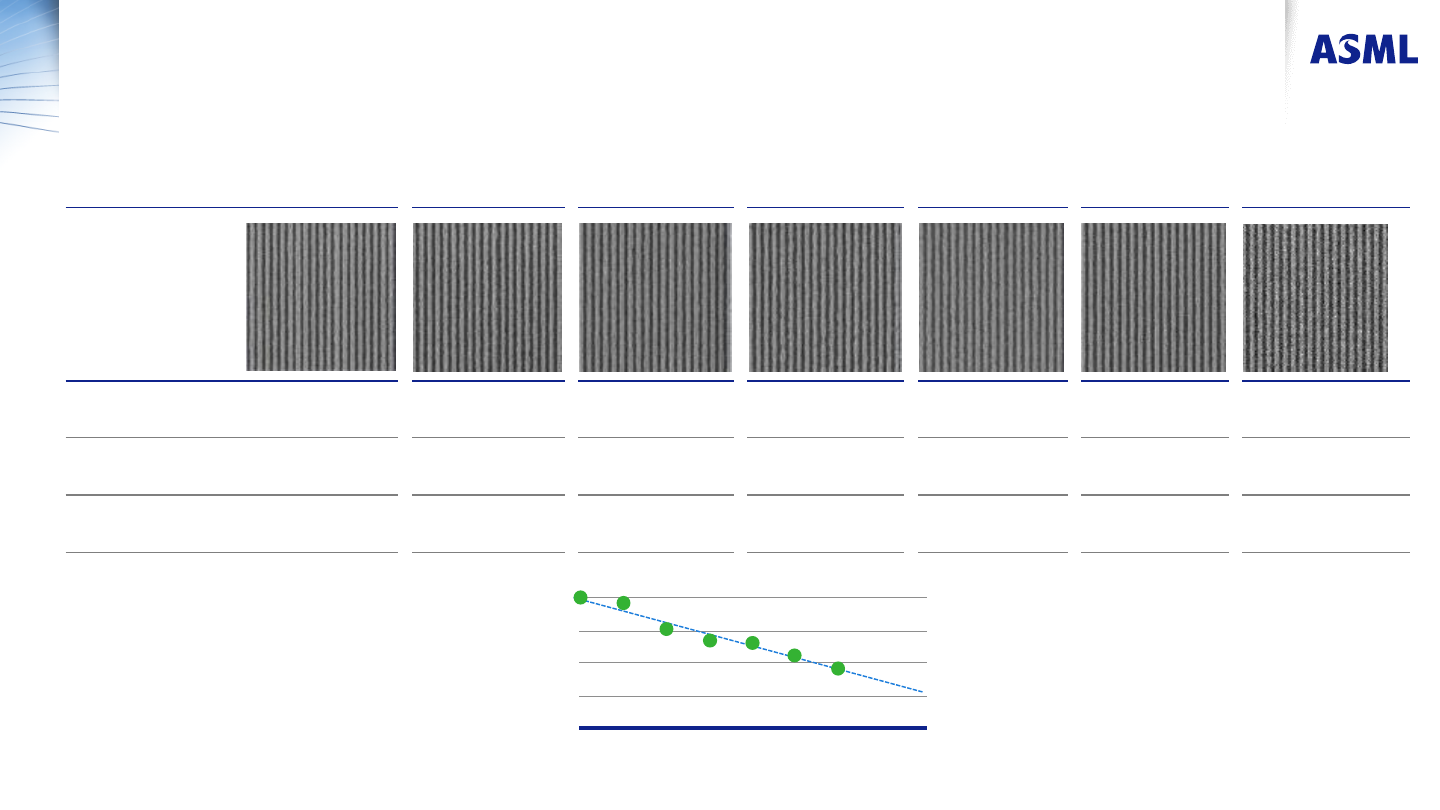

Resist improved more than 2x in the last 6 years

Improved Line Width Roughness (LWR) and dose as measured by Z-factor*

EUVJ-2107

2013 2014 2015 2016 2017 2018 2019

Dose 50mJ 58mJ 42mJ 23mJ 21mJ 38 mJ 37mJ

LWR 4.4nm 4.0nm 4.2nm 5.3nm 5.5nm 3.8 3.5

Z-factor 4.0 3.8 3.0 2.6 2.6 2.2 1.9

*Z-factor = Res

3

x LWR

2

x Dose

16nm DL horizontal; Dipole90Y

Source: ‘Progress in EUV resists towards high-NA EUV lithography’, Xiaolong Wang et al. (PSI), SPIE 2019

2013 2015 2017 2019 2021

0

1

2

3

4

Z-Factor (10 )

-8

Public

Performance of NXE:3400B in the Field

Slide 19

Public