IPC-D-279 EN.pdf - 第119页

can also be used as a process control measure once the process is under control. J-8.0 ISSUES AND CONCERNS OF TESTING J-8.1 Test Equipment The tester used with certain high- density assembly technologies may itself have …

There are also issues associated with the type of test equip-

ment used. Each tester has capabilities and limits which

can affect its ability to check product functionality. These

should be catalogued on-line and automatically enforced so

that all test programs developed will work properly with

the target test equipment. There are several software prod-

ucts available which streamline test vector generation and

simplified simulation can be useful. The major methods of

improving testability follow in the sections below.

J-7.1 Ad Hoc Techniques Test access pins, multiplexers,

control gates, test buses, embedded test software and other

cases where specific approaches are used to improve the

controllability, observability, and partitioning.

J-7.2 Structured Techniques Scan methods such as

level sensitive scan design (LSSD), scan set, and random

access scan alter sequential storage elements within the

device logic to act as serial shift registers. These scan tech-

niques allow automatic test generation and can be com-

bined with boundary-scan and built-in-self-test (BIST)

approaches for a very comprehensive approach to test.

J-7.2.1 Boundary-Scan Boundary scan is a structure

digital DFT technique which places a serial access path

(scan path) around the periphery (boundary) of the device

logic. Its main purpose is to provide test access for verify-

ing the integrity of interconnects at the assembly level by

means of a 4-wire serial bus. The boundary-scan architec-

ture allows three main types of testing.

1. External Test: This mode allows verifying the inter-

connections between the IC and external test equip-

ment or other ICs, including the circuit traces, bond

wires backplanes, and connectors. Open circuit,

bridging fault or stack fault conditions can also be

detected.

2. Internal Test: Internal test allows individual compo-

nents to be tested as though they were free-standing

devices. The large serial vectors required and lengthy

run time are drawbacks to this method. A more effec-

tive means of internal test is boundary-scan coupled

with at speed BIST circuitry.

3. Sample Mode: This feature allows monitoring of

device I/O pins during normal operation of the sys-

tem without affecting circuit operation.

Although boundary-scan is primarily aimed at dc type test-

ing the basic IEEE 1149.1/JTAG architecture can be

extended to achieve other test methods.

J-7.2.2 BIST BIST is synonymous with built-in-test

(BIT) and self-test. It can be defined as the capability of a

system to test itself with little or no external test equip-

ment, or manual intervention techniques are used to create

on-chip hardware for input stimulus generation and output

response evaluation. Functional and structural techniques

that allow circuit modified registers can be used to provide

stimulus and response capability.

J-7.2.3 Boundary-Scan Coupled with BIST Boundary-

scan coupled with BIST provides a hierarchical approach

to testing from the wafer level to system level. Test rou-

tines developed by the IC manufacturers can be reused at

all successive higher levels of assembly.

J-7.3 Resistive Testing with Flying Probes The most

straight forward method of testing is with two moving

probes using resistance to detect faults. This method elimi-

nates dependence on expensive fixtures and provides a

simple, straightforward way of testing. Probe tip designs,

mechanical stage accuracy, and pad damage issues must be

dealt with.

J-7.4 Capacitance Testing Capacitance testing is done

with a single moving probe. New capacitance measure-

ments are made with reference to an external conductive

reference plate or an internal substrate conductive plane.

The speed advantage over resistance testing is obvious

since the number of tests required is equal to the total

number of net nodes on the substrate, a linear function of

complexity.

J-7.5 Combined Resistance/Capacitance Testing To

eliminate lengthy resistance test time and improve the qual-

ity of the test method, combining both capacitance and

resistance testing can be used. When capacitance and resis-

tance instrumentation are combined for testing, it only

takes a software change to perform other tests and diagnos-

tics.

J-7.6 Glow Discharge Glow discharge testing provides a

way of optically detecting opens and shorts. The substrate

under test is placed in a chamber which is evaluated and

then back-filled with an inert gas such as argon. A single

moving probe contacts one node of each network to apply

a voltage to the net which then appears on all top surface

nodes of the net. The visible glow of each node is viewed

through a window in the top of the changer by a scanning

photometer.

J-7.7 Automatic Optical Inspection (AOI) AOI can

detect feature defects that might cause electrical opens and

shorts. AOI is computational intensive and generally uti-

lizes highly specialized image analysis data processors to

achieve acceptable inspection time. A major issue involves

achieving adequate image contrast to reduce the inspection

problem to a binary (black/white) image. AOI and non-

contact probing are desirable in situations where hard prob-

ing can cause damage which reduces process yields. AOI

July 1996 IPC-D-279

107

can also be used as a process control measure once the

process is under control.

J-8.0 ISSUES AND CONCERNS OF TESTING

J-8.1 Test Equipment

The tester used with certain high-

density assembly technologies may itself have limitations

which must be considered. As single line conductor pitch

continues to fall, it becomes increasingly difficult to probe

all points, even if they are located on an outer layer. Probe

points on the test head become increasingly fragile. Copla-

narity of the test head and assembly is also a concern.

J-8.2 Test Points The distribution of test points routed

on or brought to an outside layer is also an issue. If they

are clustered together, too much pressure may be brought

to bear on a small area of fragile substrate. In particular,

dense circuits may have difficulty placing test points for all

desired nodes on an outside layer.

J-8.3 Costs Cost issues also need to be considered.

Reducing the test probe grid below 1.25 mm results in

more expensive test fixtures. Test probes with these spac-

ings are quite fragile and may require frequent placement.

Clam shell fixtures, which can simultaneously probe both

sides of an assembly, if required, are also costly. In addi-

tion, clam shell fixtures may be subject to timing problems

since back side wires in the test fixtures may be longer than

front side ones.

J-8.4 CAD/CAE Software A host of issues are associated

with the hardware and software platform on which CAD/

CAE software runs. They are beyond the scope of this

document. However, suffice it to say that CAD/CAE soft-

ware vendors must be attentive to the changing trends in

technologies; even with a large installed base, proprietary

platforms are already proving to be obsolete.

IPC-D-279 July 1996

108

Appendix K

Design for Manufacturability and Assembly Checklist

K-1.0 SUMMARY

Definition of manufacturability: a measure of the ease or

simplicity with which a product can be manufactured or

assembled.

These guidelines deal with Design for Manufacturability

(DfM) primarily at the detailed component and process

levels and the focus is on doing things right, particularly

with respect to improving quality and reliability; if the

DfM process is used early in the design process, the focus

can be on doing the right things in terms of system organi-

zation and setting testability expectations. More benefits

are derived from early use of conceptual design and DfM

processes.

Section Topics:

• Minimize number of parts

• Minimize number of part numbers

• Design for robustness (Design of Experiments)

• Eliminate adjustments

• Design for efficient and adequate inspection and test-

ing (testability)

• Eliminate engineering changes on released products

• Make assembly easy and foolproof (Poka-Yoke)

• Use repeatable, well-understood processes

• Choose parts that can survive (are compatible with)

process operations including rework, repair and main-

tenance

• Choose or design process for compatibility with sus-

ceptible parts

• Layout parts for reliable process completion

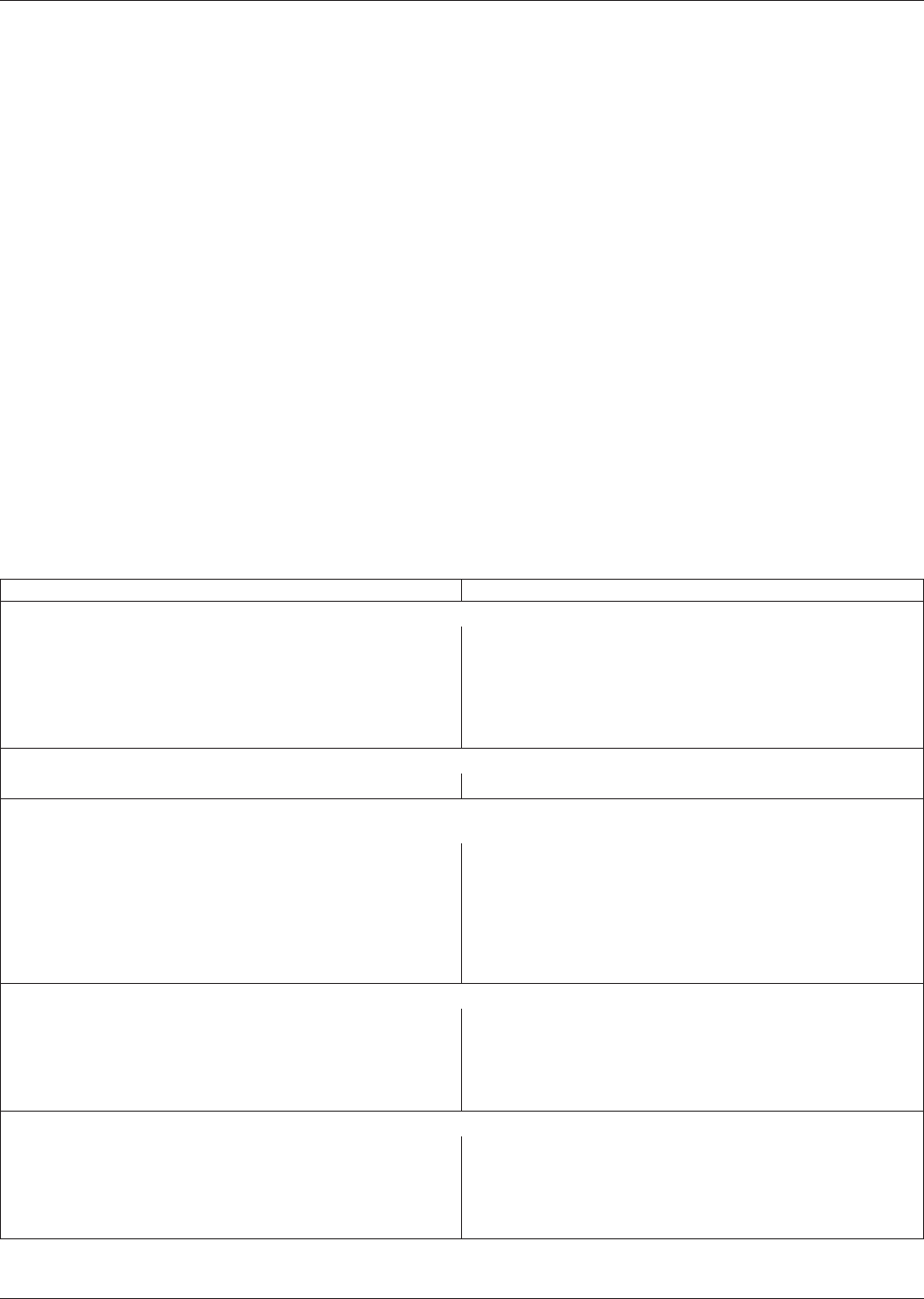

Table K-1 Checklist for Design for Manufacturability and Assembly

GUIDELINE AREA OF QUALITY/RELIABILITY IMPROVEMENT

Minimize Number of Parts

Fewer part and assembly drawings

Less complicated assemblies

Fewer parts to hold to required quality characteristics

Fewer parts to drift or fail

Fewer solder attachments to make or fail

‘Design Guidelines for Quality Improvement’

Fewer documents to control

Lower assembly error rate

Higher consistency of part quality

Higher reliability

Minimize Number of Parts

Fewer variations of like parts Lower assembly error rate

Design for Robustness (Design of Experiments)

Low sensitivity to component variability

PTH, via aspect ratio (AR) < 5:1 temperature

or use blind/buried vias

Use standard or preferred parts (EIA/JEDEC registered)

Use compatible SM land patterns (IPC-SM-782)

Higher first-pass yield and less degradation of

performance over time

Less sensitivity to cycling and thermal shock, lower failure rate

Fewer new failure modes and mechanisms

Fewer suppliers to manage

Widen process window

Increase assembly yield

Eliminate Adjustments

No assembly adjustment errors

Eliminate adjustable components with high failure rates

Eliminate change in adjustments under vibration and shock

Provide adjustments and compensation through software

Consider digitally switched resistor network

Higher first-pass yield

Lower failure rate

Design for Efficient and Adequate Inspection and Testing (Testability)

Less mistaking ‘‘good’’ for ‘‘bad’’ product and vice versa

Less effort to locate defects

Better control over rework/repair

Truer assessment of quality, less unnecessary rework

Faster diagnosis to root cause

Less service/maintenance time

More ‘‘up’’ time

Less part damage

July 1996 IPC-D-279

109