IPC-D-279 EN.pdf - 第68页

reliability of these PTVs significantly . Therefore, it is best to avoid the possibility of these stress concentrations all together by tenting the PTVs. However , it needs to be emphasized, that this issue is important o…

with 10 being perfect, and is a measure of the quality of the

plated copper deposit in terms of its material properties

relative to those of a corresponding foil sample plated onto

a plating mandrel. This index needs to be established by

experience with PTVs in coupons or MLBs fatigued to

failure.

B-3.0 DfR-PROCESS

A successful ‘Design for Reliability’-process requires that

a number of issues be addressed at the design stage. The

generally applicable guidelines for the DfR-process are;

1) Keep PTV diameters as large as possible and the

MLB thickness/PTV diameter aspect ratio as small

as possible;

2) Require a nominal copper deposit thickness of 30 µm

to obtain actual plating thicknesses in the range of 25

to 40 µm;

3) Use E3 copper foil for the signal, power, and ground

layers for aspect ratios larger than 3:1;

4) Tent PTVs for applications with severe operational

loading conditions (see Table B-2) with solder mask

to prevent solder from partially filling the PTVs and

causing stress concentrations.

It is much more difficult to plate consistent high quality

copper deposits into small-diameter PTVs using standard

electrolytic processes. Also, smaller diameter PTV barrels,

especially in thicker MLBs, are subjected to higher loading

conditions.

A plating thickness of ~25 µm has been found to be the

minimum thickness which gives good reliability; a plating

thickness of ~40 µm is optimum from a reliability perspec-

tive. Plating thicknesses greater than that tend to promote

shoulder fractures (see Fig. B-2).

The quality of the copper foil for the signal, power, and

ground layers is of importance for aspect ratios larger than

about 3:1. Standard E1 copper foil [Ref. B-7: 14] has a

coarse columnar grain structure with the grain boundaries

perpendicular to the foil surfaces and has an elongation

requirement of only 2%. Thus, brittle E1 vendor foil can

lead to signal layer fractures and shoulder cracks as illus-

trated in Figure B-2. ‘High Temperature Elongation’ -E3

copper foil is recommended for PTVs with aspect ratios

larger than about 3:1.

Tenting the PTVs is a prudent and pragmatic decision.

PTVs entirely filled with solder certainly are more robust

and reliable than PTVs without solder; the problem is that

it cannot be guaranteed, that all the PTVs will be entirely

filled with solder. Partially solder-filled PTVs have stress

concentrations where the transition from fully filled to par-

tially filled occurs; these stress concentrations reduce the

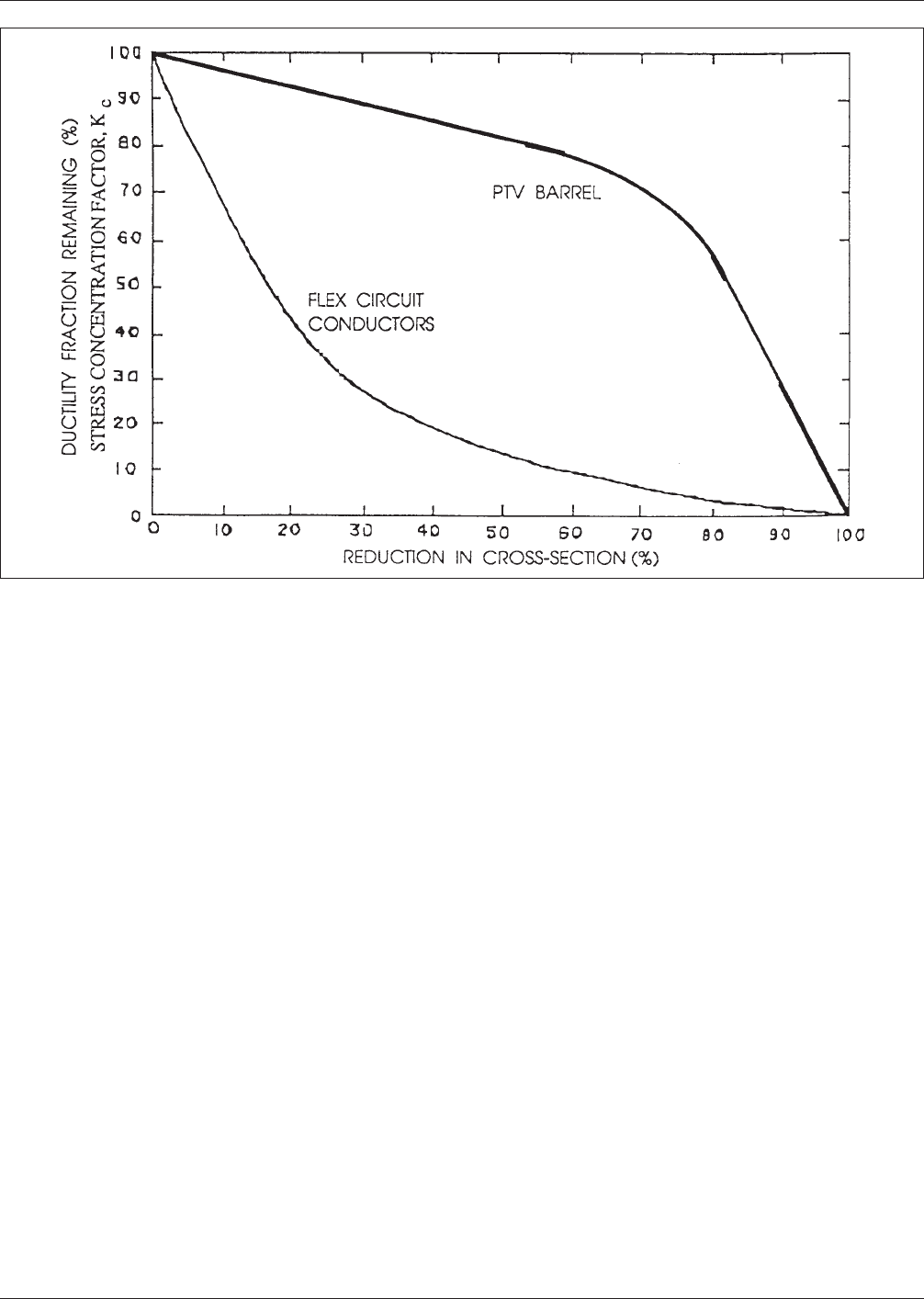

Figure B−3 Reduction of Available Copper Ductility Due to Localized Nicks Reducing the Width of the Flex Circuit

Conductors [Ref. B-7: 25] and PTV Stress Concentration Factor, K

c

.

IPC-D-279 July 1996

56

reliability of these PTVs significantly. Therefore, it is best

to avoid the possibility of these stress concentrations all

together by tenting the PTVs. However, it needs to be

emphasized, that this issue is important only for severe use

conditions with temperature cycles of about ∆T≥50°C, as

can be seen in Table B-2.

In Table B-1 in Section B-1.2.2 the minimum fatigue duc-

tilities resulting from two accelerated fatigue tests of PTVs

in MLBs are given. These estimates of the copper deposit

properties in the PTV barrels are used in Table B-2 to esti-

mate the minimum fatigue lives for a number of typical

electronic use environments. The fatigue lives are given

together with the pertinent information on the use condi-

tions and the resulting stresses and strains.

The results in Table B-2 indicate that the PTVs of good

quality do not constitute a reliability threat to most product

applications in the field. Only for the more severe use envi-

ronments would premature failures be anticipated. How-

ever, the results in Table B-2 would change drastically for

PTVs of low quality.

The DfR-process needs to emphasize a physics-of-failure

approach. The process might involve the following steps:

A. Identify Reliability Requirements—

expected design life and acceptable cumulative fail-

ure probability at the end of this design life;

B. Identify Loading Conditions—

use environments (e.g., IPC-SM-785) and thermal

gradients due to power dissipation;

C. Identify/Select Assembly Architecture—

substrate selections, material properties (e.g., CTE),

PTV diameter, aspect ratio;

D. Assess Reliability—

determine reliability potential of the designed assem-

bly and compare to the reliability requirements using

the approach shown here; this process may be itera-

tive;

E. Balance Performance, Cost and Reliability Require-

ments.

B-4.0 CRITICAL FACTORS FOR EMERGING ADVANCED

TECHNOLOGIES

The emerging advanced technologies are characterized by

denser packaging resulting in ever smaller structures. Thus,

the temptation exists to drive the PTV diameters ever

smaller and the aspect ratios higher. The DfR principles

detailed in Section B-3.0 need to be kept in mind in the

design and application of these emerging technologies.

B-5.0 VALIDATION AND QUALIFICATION TESTS

Validation and qualification tests have not been established

for PTVs. However, the test procedures used in the IPC

round robin program reported in IPC-TR-579, Round

Robin Reliability Evaluation of Small Diameter Plated

Through Holes in Printed Wiring Boards [Ref. B-7: 2],

could be utilized for this purpose.

Efforts are underway within the IPC via a round robin test

program to establish both qualitative and quantitative cor-

relation for a number of promising test methods.

B-6.0 SCREENING PROCEDURES

The crucial task is the elimination of the MLBs with thin-

plated PTVs without significantly affecting the remainder

of the MLBs. The fact that the defects not only involve

very thin plating (<10 µm), but occur in conjunction with

substantial stress/strain concentrations, makes this task pos-

sible.

An Environmental Stress Screening (ESS) could employ

the same test setup as the Hot Oil Test (IEC Specification

362-2, Test C) [Ref. B-7: 2], for three (3) to five (5) cycles.

Thus, together with the solder reflow operations necessary

for production, the MLBs would experience between eight

(8) to ten (10) such temperature excursions.

Given the result, based on standard IEC test criteria, that

the life under these loading conditions is 32 cycles, this

would consume between 25 and 30 % of the MLBs lives.

Considering the results in Table B-2, that still would leave

adequate life for most use environments.

B-7.0 REFERENCES

1. ‘‘Leading Edge Manufacturing Technology Report,’’

IPC Technical Report IPC-TR-578, The Institute for

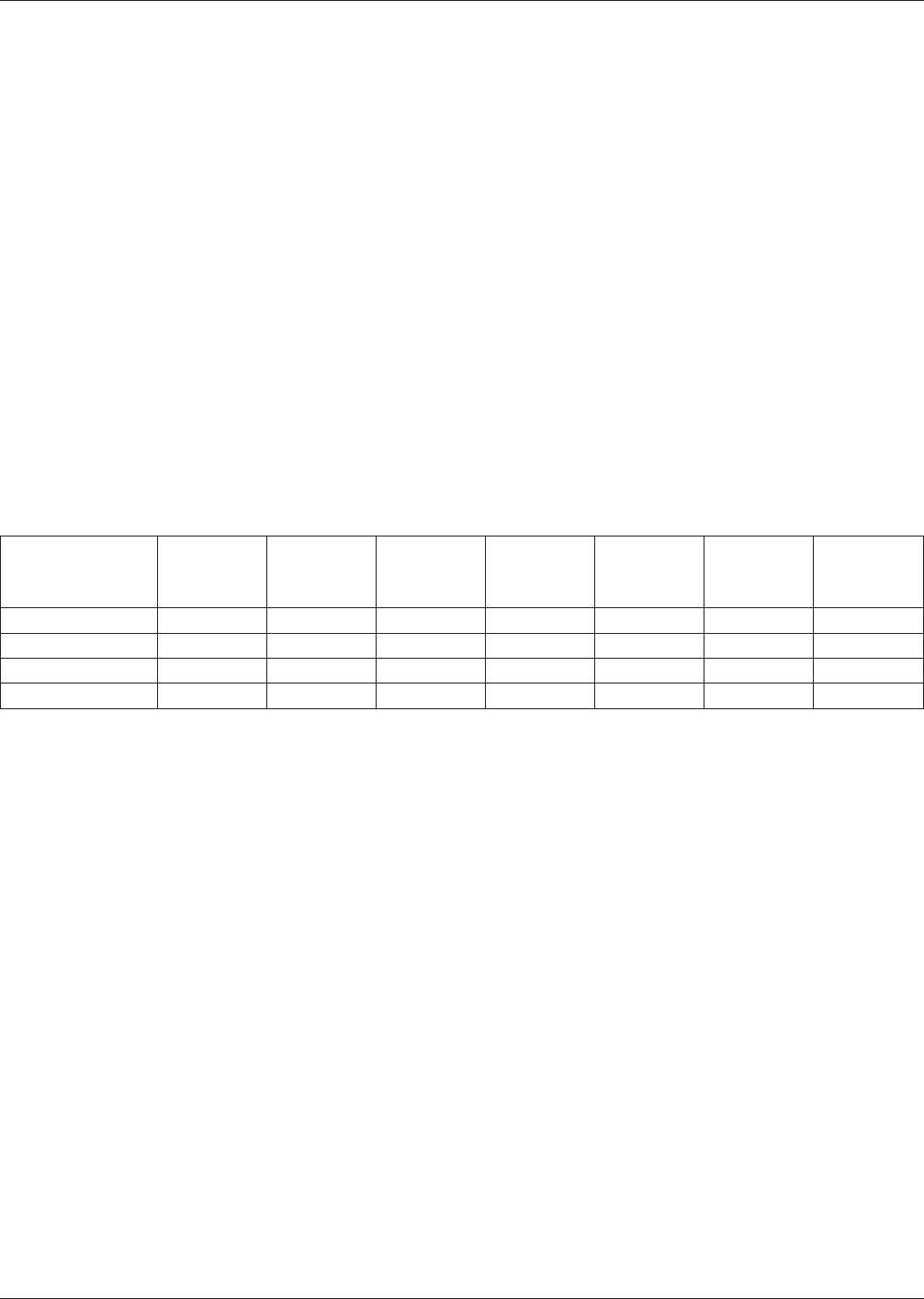

Table B−2 Estimates of the Fatigue Life and Time to Failure of PTVs in Some Typical Use Environments from Table A-1

Used

Environment

∆T

[°C]

Estimated

Maximum

Annual

Cycles

Barrel Stress

σ

[MPa/ksi]

Strain Range

∆ε

[%]

Effective

Strain Range

∆ε

max

(eff)

[%]

Minimum

Fatigue Life

[cycles]

Estimated

Time to First

Failure

[years]

Computers 20 1460 67/9.7 0.08 0.20 8.0X10

6

5 500

Telecomm 35 365 117/16.9 0.14 0.35 75 000 205

Industrial 60 250 173/25.1 0.28 0.71 2 900 12

Automotive 80 365 174/25.2 0.38 0.95 1 200 3.3

July 1996 IPC-D-279

57

Interconnecting and Packaging Electronic Circuits,

Northbrook, IL, September 1984.

2. ‘‘Round Robin Reliability Evaluation of Small Diam-

eter Plated Through Holes in Printed Wiring Boards,’’

IPC Technical Report IPC-TR-579, The Institute for

Interconnecting and Packaging Electronic Circuits,

Northbrook, IL, September 1988.

3. Oien, M. A., ‘‘A Simple Model for the Thermo-

Mechanical Deformations of Plated-Through-Holes in

Multilayer Printed Wiring Boards,’’ Proc. 14th Ann.

IEEE Reliability Physics Symp. pp. 121-128, 1976.

4. Oien, M. A., ‘‘Methods of Evaluating Plated-Through-

Hole Reliability,’’ Proc. 14th Ann. IEEE Reliability

Physics Symp., pp. 129-131, 1976.

5. Engelmaier, W., and T. Kessler, ‘‘Investigation of Agi-

tation Effects on Electroplated Copper in Multilayer

Board Plated-Through Holes in a Forced-Flow Plating

Cell,’’ J. Electrochemical Soc., Vol. 125, No. 1, Janu-

ary 1978, pp. 3643.

6. Mirman, B. A., ‘‘Mathematical Model of a Plated-

Through Hole Under a Load Induced by Thermal Mis-

match,’’ IEEE Trans. Comp., Hybrid, Manuf, Technol-

ogy, Vol. 11, No. 4, December 1988, pp. 506-511.

7. Iannuzzelli, R., ‘‘Predicting Plated-Through-Hole Reli-

ability in High Temperature Manufacturing Pro-

cesses,’’ IPC Annual Meeting, Boston, MA, April

1990.

8. Ozmat, B., H. Walker, and M. Elkins, ‘‘A Nonlinear

Thermal Stress Analysis of the Plated Through Holes

of Printed Wiring Boards,’’ Proc. Int. Electronic Pack-

aging Conf. (IEPS). Marlborough, MA, September

1990.

9. Bhandarkar, S. M., A. Dasgupta, D. Barker, M. Pecht,

and W. Engelmaier,‘‘Influence of Selected Design

Variables on Thermo-Mechanical Stress Distributions

in Plated-Through-Hole Structures,’’ ASME J.Elec-

tronic packaging, Vol. 114, No. 1, March 1992, pp.

8-13.

10. Engelmaier, W., ‘‘Manufacturing and Reliability Issues

of Small Diameter/High-Aspect-Ratio Plated-Through-

Holes and Vias,’’Workshop Notes, Engelmaier Associ-

ates, Inc., 1991.

11. Engelmaier, W., ‘‘Results of IPC Copper Foil Ductility

Round Robin Study,’’ IPC Technical Report IPC-TR-

484, The Institute for Interconnecting and Packaging

Electronic Circuits, Lincolnwood, IL, April 1986.

12. ‘‘Flexural Fatigue and Ductility, Foil,’’ Test Method

2.4.2.1, Test Methods Manual IPC-TM-650, The Insti-

tute for Interconnecting and Packaging Electronic Cir-

cuits, Northbrook, IL.

13. ‘‘Standard Test Method for Ductility Testing of Metal-

lic Foil,’’ ASTM E 796-88, Annual Book of ASTM

Standards, ASTM, Philadelphia, PA.

14. ANSI/IPC-MF-150F, ‘‘Metal Foil for Printed Wiring

Applications,’’ The Institute for Interconnecting and

Packaging Electronic Circuits, Lincolnwood, IL, Octo-

ber 1991.

15. Cygon, M., ‘‘High Performance Materials for PCBs,’’

Circuit World, Vol. 19. No. 1, October 1992, pp. 14-18.

16. Olson, L.D., ‘‘Printed Wiring Boards: Conventional

Plastic Composite Boards’ Resins and Reinforce-

ments,’’ chapter in Electronics Materials Handbook,

Vol. I Packaging, ASM International, Materials Park,

Ohio, 1989, pp. 534-537.

17. Ozawa, S., T. Takeda and T. Ohtori, ‘‘Epoxy Resin

Multilayer Materials,’’ Proc. Printed Circuit World

Cony. VI, San Francisco, May 1993, pp. T5/1-T5/9.

18. Davis, B., ‘‘A Tour Through the Board Manufacturing

Process,’’ Printed Circuit Design. Vol. 10, No. 8,

August 1993, pp. 11-14.

19. Lampe, J. W., ‘‘The Interrelationships of Design,

Materials, and Processes for Surface Mount Assem-

blies in Military Applications,’’ Surface Mount Tech-

nology. Vol. 3, No. 7, November 1989, pp. 22-27.

20. Hu, M., ‘‘Choosing Laminates,’’ Advanced Packaging,

Vol. 2, No. 5, Fall 1993, pp. 16-18.

21. Engelmaier, W., ‘‘A New Ductility and Flexural

Fatigue Test Method for Copper Foil and Flexible

Printed Wiring,’’ IPC Technical Paper IPC-TP-204,

The Institute for Interconnecting and Packaging Elec-

tronic Circuits, Lincolnwood, IL, April 1978.

22. Engelmaier, W., ‘‘A Method for the Determination of

Ductility for Thin Metallic Materials,’’ Formability of

Metallic Materials-2000 A.D., ASTM STP 753, J. R.

Newby and B. A. Niemeier, eds., American Society for

Testing and Materials, 1982, pp. 279-295.

23. Manson, S.S., Thermal Stress and Low Cycle Fatigue,

McGraw-Hill, New York, 1966.

24. Engelmaier, W., ‘‘Designing Flex Circuits for

Improved Flex Life,’’ Proc 12th Electrical/Electronics

Insulation Conf., Boston, MA, November 1975.

25. Engelmaier, W., ‘‘Flexibility Considerations in the

Design of Flexible Printed Wiring,’’ Section 6.2.1.2,

IPC Printed Wiring Design Guide IPC-D-330, The

Institute for Interconnecting and Packaging Electronic

Circuits, Lincolnwood, IL, January 1982.

IPC-D-279 July 1996

58