IPC-D-279 EN.pdf - 第75页

13. Klein W assink, R. J., ‘ ‘Soldering in Electronics,’ ’ 2nd ed., Electrochemical Publications, Ltd., Isle of Man, UK, 1989, pp. 215-216. 14. Sinnadurai, F . N. ‘ ‘Handbook of Microelectronics Packaging and Interconnec…

Contamination The presence of contamination on the sur-

face will increase the moisture absorption. The critical rela-

tive humidity can be lowered by the presence of contami-

nants. The nature of these contaminants will determine how

much moisture is absorbed at a given humidity level. If

these contaminants are ionic in nature, they can enhance

electrochemical reactions that occur in the presence of a

bias voltage.

Voltage The bias voltage applied across the insulator will

set-up a response in the dipolar polymer substrate. In per-

forming SIR testing, it is important that the bias voltage

chosen is realistic as it relates to the actual operating and

use conditions of the electronic assembly. Typical test

methods require 45-50 V bias because this represents a

moderate accelerating condition relative to the +/- 15 V

circuits common in telecommunication hardware. Exces-

sively high voltage tests for routine circuits can lead to

damage mechanisms and failure not representative of pro-

duct use.

C-6.0 SCREENING PROCEDURES

For the threats to reliability from low SIR and CAF forma-

tion no effective screening procedure exists. The best that

can be done is following the DfR recommendations in Sec-

tion C-3.0 and the testing of representative samples using

the test procedures discussed in Section C-5.0.

C-7.0 REFERENCES

1. Engelmaier, W., ‘‘On the Parametric Temperature/

Humidity Dependence of Insulation Resistance of

Covercoated Fine-Line Flexible Printed Wiring,‘‘ Proc.

Nat, Electronic Packaging and Production Conf,

(NEPCON West), Anaheim, CA. February 1976, p. 87.

2. ‘‘D-C Resistance or Conductance of Insulating Materi-

als,’’ ASTM D 257-78. Annual Book of ASTM Stan-

dards, ASTM, Philadelphia, PA.

3. Gorondy, E. J., ‘‘Surface Insulation Resistance Part I:

The Development of an Automated SIR Measurement

Technique,‘‘ IPC Technical Paper IPC-TP-518, The

Institute for Interconnecting and Packaging Electronic

Circuits, Lincolnwood, IL, September 1984.

4. Zado, F. M., ‘‘Effects of Non-Ionic Water Soluble Flux

Residue,’’ Western Electric Engineer, Vol. 1, No. 1,

1983.

5. Kawanobe, T., and K. Otsuka, ‘‘Metal Migration in

Electronic Components,’’ Proc. 32nd Electronic Com-

ponents Conf., San Diego, CA, May 1982, pp. 220-

228.

6. Uhlig, H. H. ‘‘Corrosion and Corrosion Control,’’ 2nd

ed., John Wiley & Sons, Inc., New York, NY, 1971,

p.322.

7. Lando, D. J., J. P. Mitchell, and T. L. Welsher, ‘‘Con-

ductive Anodic Filaments in Reinforced Polymeric

Dielectrics: Formation and Prevention,’’ Proc. 17th

Ann. Reliability Physics Symp., April 1979, pp. 51-63.

8. Augis, J. A., D. G. DeNure, M. J. LuValle, J. P. Mitch-

ell, M. R. Pinnel, and T. L. Welsher, ‘‘A Humidity

Threshold for Conductive Anodic Filaments in Epoxy

Glass Printed Wiring Boards,’’ Proc. 3rd Int, SAMPE

Electronics Conf.. June 20-22, 1989, pp. 1023-1030.

9. Ready, W. J., S. R. Stock, and L. J. Turbini, unpub-

lished results.

10. Turbini, L. J., unpublished work.

11. Cotter, M., and W. Engelmaier, unpublished results.

12. LuValle, M. J., T. L. Welsher, and J. P. Mitchell, R. J.,

‘‘A New Approach to the Extrapolation of Accelerated

Life Test Data,’’ Proc. 5th Int. Reliability and Main-

tainability Conf., Biarritz, France, 1986, pp. 630-635.

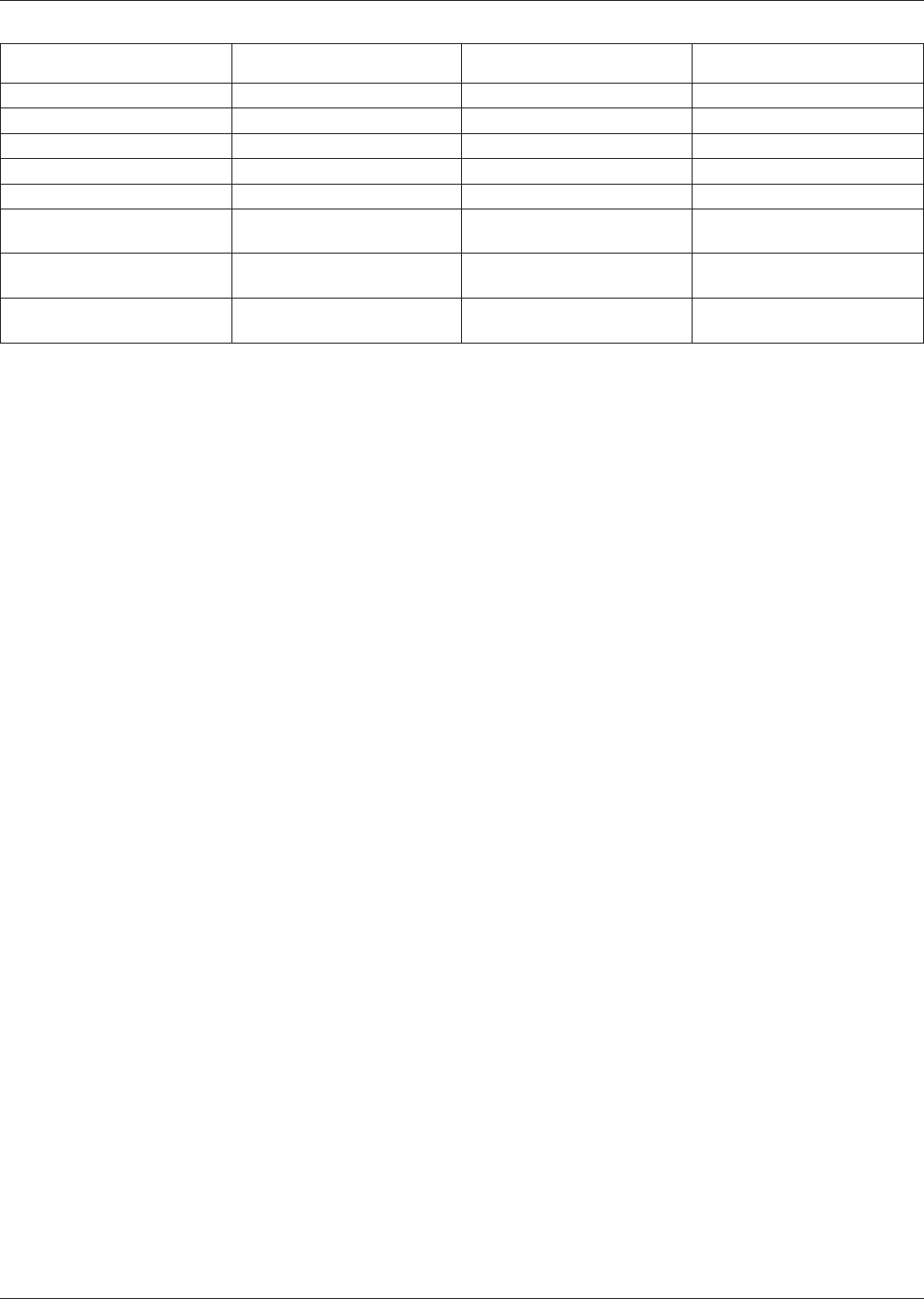

Table C−1 SIR Test Parameters for Some Industry Tests

Parameters

IPC-TM-650

Solder Flux

Bellcore

SIR

Bellcore

Electromigration

Test Voltage 100 V 100 V 45 to 100V

Bias Voltage 50 V 50 V 10 V

Polarity Reverse Reverse Same

Environment 85°C/85%RH 35°C/85%RH 85°C/85%RH

Duration 7 days 4 days 500 hours

Lines/Spacing 0.4/0.5 mm 0.64/1.27 mm

0.32/0.32 mm

0.32/0.32 mm

Number of Squares ~1000 ~100

~500

~500

Failure Criteria 100 MΩ 10

5

MΩ

2x10

4

MΩ

SIR less than 1 decade

decline

July 1996 IPC-D-279

63

13. Klein Wassink, R. J., ‘‘Soldering in Electronics,’’ 2nd

ed., Electrochemical Publications, Ltd., Isle of Man,

UK, 1989, pp. 215-216.

14. Sinnadurai, F. N. ‘‘Handbook of Microelectronics

Packaging and Interconnection Technologies,’’ ed.,

Electrochemical Publications, Ltd., Ayr, Scotland,

1985, p. 271.

15. Lahti, J. N., R. H. Delany, and J. N. Hines, ‘‘The Char-

acteristic Wearout Process in Epoxy-Glass Printed Cir-

cuits for High Density Electronic Packaging,’’ Proc.

17th Ann. Reliability Physics Symp., April 1979, pp.

39-43.

16. Welsher, T. L., J. P. Mitchell, and D. J. Lando, ‘‘CAF

in Composite Printed-Circuit Substrates: Characteriza-

tion, Modeling and a Resistant Material,’’ Proc. 18th

Ann, Reliability Physics Symp., April 1980, pp. 235-

237.

17. Welsher, T. L., J. P. Mitchell, and D. J. Lando, ‘‘Con-

ductive Anodic Filaments (CAF): An Electrochemical

Failure Mechanism of Reinforced Polymeric Dielec-

trics,’’ Proc. Ann. Electrical Insulation and Dielectric

Phenomena Conf., 1980, pp. 234-239.

18. ‘‘Generic Physical Design Requirements for Telecom-

munications Products and Equipment,’’ Bellcore Tech-

nical Reference TR-NWT-000078, Issue 3. December

1991.

19. ‘‘Surface Insulation Resistance, Fluxes,’’ Test Method

2.6.3.3. Test Methods Manual IPC-TM-650, The Insti-

tute for Interconnecting and Packaging Electronic Cir-

cuits, Lincolnwood, IL.

20. Krumbein, S. J., ‘‘Metallic Electromigration Phenom-

ena,’’ IEEE Trans. Components, Hybrids, and Manu-

facturing Technology, Vol. 91, CHMT-11, No. 1,

March 1988, pp. 5-15.

21. Cvijanovich, G. B., and A. R. Baily, ‘‘Technical Report

on the Conductivity and Electrolytic Properties of

Adsorbed Layers of Water,‘‘ Advanced Product and

Manufacturing Technologies Dept., AMP Inc., Harris-

burg, PA.

22. Howard, R. W., ‘‘Electrochemical Model for Corrosion

of Conductors on Ceramic Substrates,’’ IEEE Trans,

Components, Hybrids, and Manufacturing Technology.

Vol. CHMT-4, No. 4, December 1981, pp. 520-525.

23. Jennings, C. W., ‘‘Effect of High Moisture Environ-

ments of Printed Wiring Board Insulation,’’ Proc.

Printed Circuit World Convention II (IPC), June 1981.

24. Sinclair, J. D., ‘‘An Instrumental Gravimetric Method

for Indexing Materials, Contaminants and Corrosion

Products According to Their Hygroscopicity,’’ J. Elec-

trochemical Society. Solid State Science and Technol-

ogy, May 1978, pp. 734-742.

25. DerMarderosian, A., and C. Murphy, ‘‘Humidity

Threshold Variation for Dendritic Growth on Hybrid

Substrates,’’ Proc, 15th Ann. Reliability Physics

Symp., April 1977, pp. 92-100.

26. Lefebvre, D. R., K. M. Takahashi, A. J. Muller, and V.

R. Raju, J. Adhesion Science and Technology, Vol. 5,

No. 3, 1991, pp. 201-227.

IPC-D-279 July 1996

64

Appendix D

Thermal Considerations

D-1.0 GENERAL

The designer of an SM PWA will be constrained by several

external thermal factors:

A. The preference for cost and noise reasons is to cool

by free convection or by conduction of heat to the

outside atmosphere through thermally conducting

copper planes, metallic cardguides and thermally

conducting structural ribs in the system chassis.

B. The preference for contamination and corrosion con-

trol is to seal the PWA away from external air.

C. The heat densities and hotspot temperatures may

require active (forced) cooling with media such as air

or heat control fluids moved by fans or pumps.

D. The spacing between PWAs, the component spacings

and geometries, as well as air velocities may result in

either laminar or turbulent flows, affecting both heat

removal from heat dissipaters and heat transfer to

thermally sensitive components.

The primary thermal parameter which the designer must

address is the temperature of the junction or active film of

the component; both the absolute maximum or peak tem-

perature and the steady state operating temperature limits

imposed by the component manufacturer (as modified by

derating protocols) must be observed. The secondary ther-

mal parameter is the solder joint temperature since large

temperature swings in service will subject the joint to con-

ditions leading to cyclic fatigue, and long service times at

high temperatures will grow copper-tin intermetallic com-

pounds. See also IPC-SM-785, IPC-D-275, and IPC-SM-

782.

For near-eutectic tin/lead solders - the most commonly

used solders for surface mounted assemblies - good engi-

neering practices result in typical operating temperatures of

about 70°C. Higher levels of temperature are associated

with faster aging of the solder joints due to metallurgical

changes of the material structure and composition. Cyclic

variations of the joint temperature are associated with

fatigue degradation, solder being the compliant part of the

system which has to accommodate relatively large differen-

tial expansions of the different materials. The fatigue life of

the system is dictated primarily by the temperature swing,

dwell time and lead compliancy and it is less dependent on

the absolute value of temperature and the rise time neces-

sary to reach the extreme values, providing that the varia-

tion in temperature is slower than 30°C per minute. These

factors show the importance of determining the accurate

thermal conditions − both maximum static temperature and

cycling parameters − at the solder joint layer.

Variation of the external (outside of the equipment enclo-

sure) ambient temperature is one of the multitude of factors

that will determine the actual temperature cycle a specific

surface mounted device will see in operation. Very simple

equipment, powered continuously at constant power will

see the same temperature swings as the external ambient.

In some cases, the system designer introduces built-in

means of reducing the temperature swing inside the cabi-

net, such as fans activated when the inlet air temperature

exceeds certain limits or inlet air heaters which are

activated when inlet air temperature drops below certain

limits.

In many applications, the variation of the temperature

inside the electronic enclosure is generated by variations of

the power dissipated by the electronics itself. Examples of

this type of behavior are on/off periods for the system or

fluctuations in the power dissipation as in telecommunica-

tion equipment due to variations in the number of simulta-

neous calls passing through the system. Relatively large

temperature variations could be generated inside the system

between the periods with high traffic, mainly during the

working hours, and the periods with low traffic, usually

evening or night hours, even though the system is main-

tained inside an air conditioned room with practically no

ambient temperature variations. A device mounted down-

stream of a high power dissipator sees a temperature varia-

tion related to the variation of the temperature of the ther-

mal wake produced by the power dissipator even though

the temperature inside the enclosure is maintained constant.

In most applications, the temperature variations at a par-

ticular component in a system results from a combination

of system-external and system-internal temperature varia-

tions combined with power dissipation fluctuations within

the component. It follows that different devices inside the

same system might be subjected to very different tempera-

ture cycles. In order to assess the reliability of the solder

joints, the designer must perform a complete thermal

analysis at the device level.

D-2.0 THERMAL ANALYSIS AT THE DEVICE LEVEL

The best way of understanding the different factors that

impact the device temperature and implicitly the system

reliability, is to express the junction temperature on the

silicon, T

j

, as a summation of temperatures rise at different

levels of integration in the system

T

j

=T

a

+ ∆T

CA

+ ∆T

BL

+ ∆T

P

+ ∆T

TW

These factors are discussed in D-2.1 through D-2.5 below.

D-2.1 The Ambient Temperature of an Electronic Sys-

tem (T

a

) The ambient temperature of an electronic system

is defined as the average temperature monitored outside the

July 1996 IPC-D-279

65