CAN Bus Workshop_Version 03__06-2008_EN.pdf - 第34页

1 - 8 S tudent Gu ide CAN BUS Wor kshop 2 Commun icatio n and C ontrol Editio n 06/200 8 8 2.2.1.1 CAN Bus protocol Fig. 2.2 - 5 CA N-bus protocol Start : This bit ind icates t he begi nning o f a teleg ram and i s a dom…

1 - 7

Student Guide CAN BUS Workshop

Edition 06/2008 2 Communication and Control

7

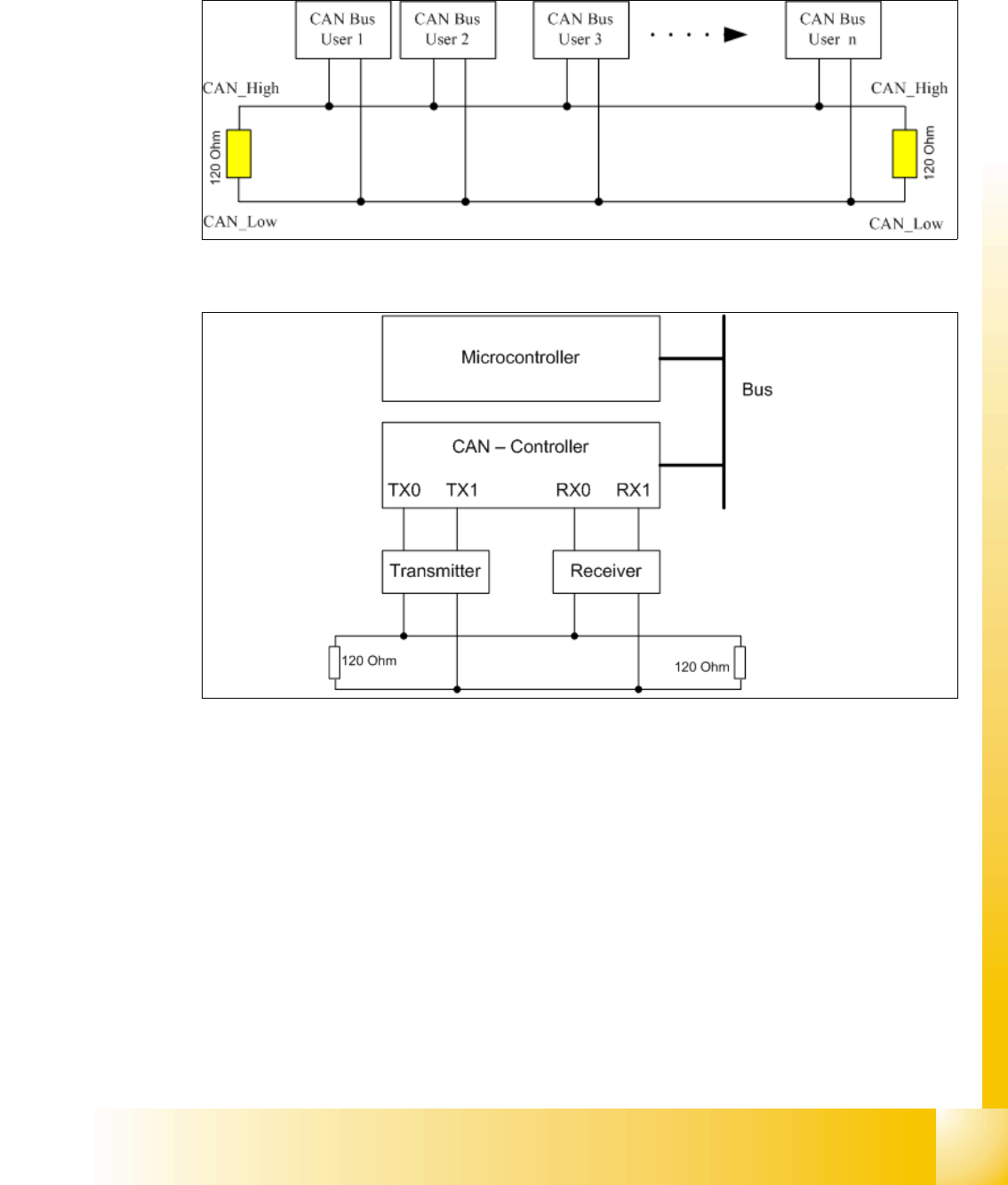

2.2.1 General structure

The CAN Bus is a decentral multi-master bus. The data are transmitted via the differential voltage

of the two CAN_High and CAN_Low lines, which are each fitted with a terminating resistance of

120 Ohm.

Fig. 2.2 - 3 CAN Bus structure

Fig. 2.2 - 4 CAN Bus -Controller and Microcontroller

Legend

– Microcontroller: Exchanges data with the CAN controller

– CAN controller: Adds the data frame, establishes the connection and manages errors.

– Transmitter/receiver: Adjusts the level (driver levels)

Each bus node has a CAN controller, which can transmit and receive data if the bus is free.

This CAN controller communicates with a microcontroller. The microcontroller steers and controls

the relevant CAN bus nodes.

A CAN Bus node can only transmit if the bus is free i.e. if there is no communication taking place

with other nodes. Access to the CAN BUS is fixed in the CAN protocol (identifier). This results in

differing priorities among the individual CAN bus nodes.

1 - 8

Student Guide CAN BUS Workshop

2 Communication and Control Edition 06/2008

8

2.2.1.1 CAN Bus protocol

Fig. 2.2 - 5 CAN-bus protocol

Start: This bit indicates the beginning of a telegram and is a dominant bit. After this bit is set, no

other user of the CAN bus is able to send.

Address field (11 bit identifier): The 11 bit address identifier value determines the bus access.

The lower value has the highest priority.

Control field: The 4 lowest bits in the 6 bit field show the data length of the following data field in

bytes (DLC: Data Length Code.

Data field: Contains the information actually required and can be from 0 byte to 8 byte. The trans-

fer of a byte begins with the most significant bit (the bit with the highest value).

Data control field CRC: Consists of a 15 bit check sequence (CRC sequence + CRC delimiter =

CRC Field - Cyclic Redundancy Check) and a recessive delimiter bit. The redundant information

in the control sequence allows the receiver to check whether the message received has been fal-

sified by interference.

End: Each data telegram is terminated by a sequence of 7 recessive bits.

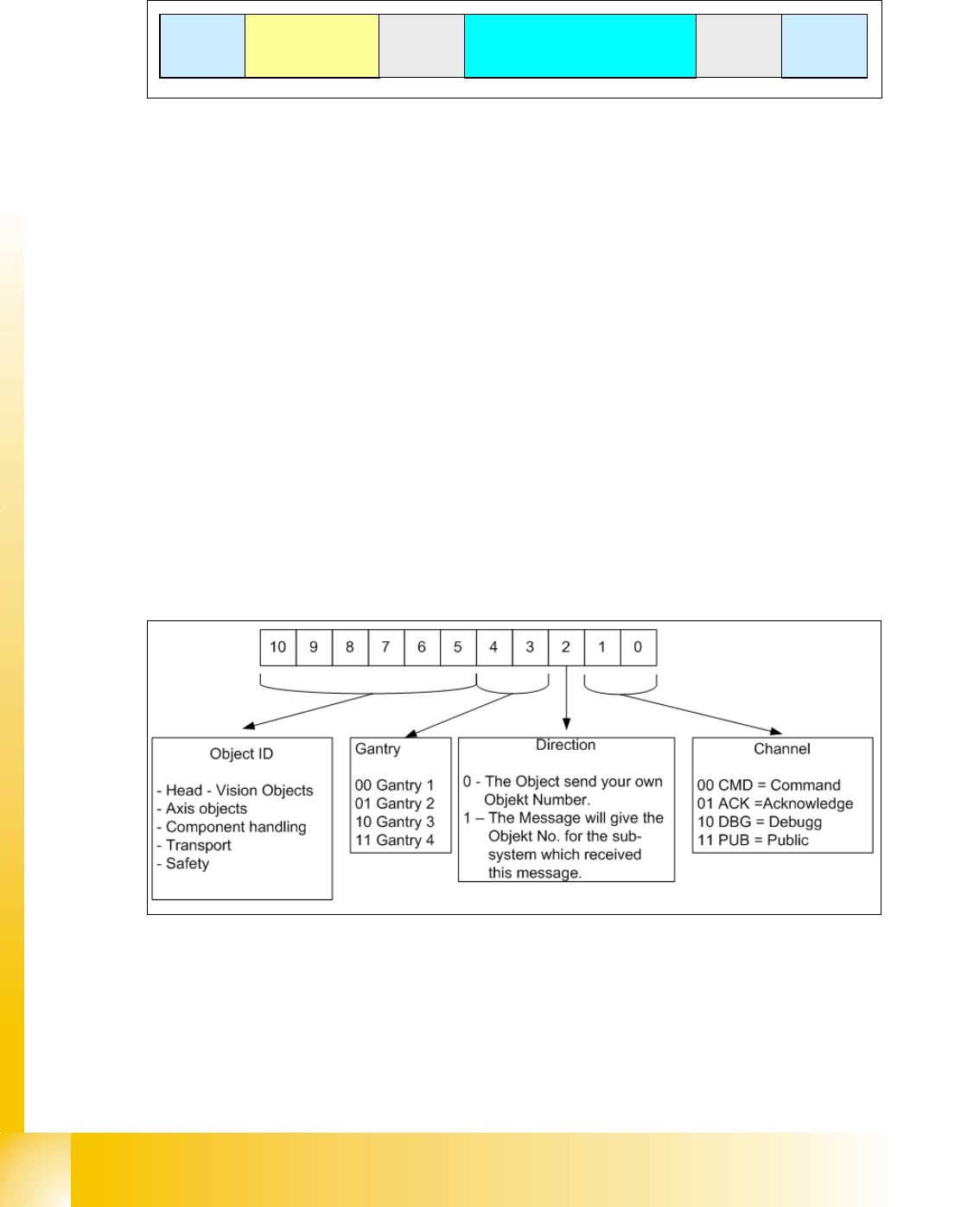

2.2.1.2 11 Bit Identifier

Fig. 2.2 - 6 11 bit identifier

The CAN bus system is using the 11 Bit identifier for addressing the different CAN objects

An 11 Bit identifier (address) identifies the type, priority, source and /or target of the message.

This identifier also controls the bus access (arbitration).

start

address

(11 bit identifier)

control

information.

data (0-8 bytes user information) CRC

end

1 - 9

Student Guide CAN BUS Workshop

Edition 06/2008 2 Communication and Control

9

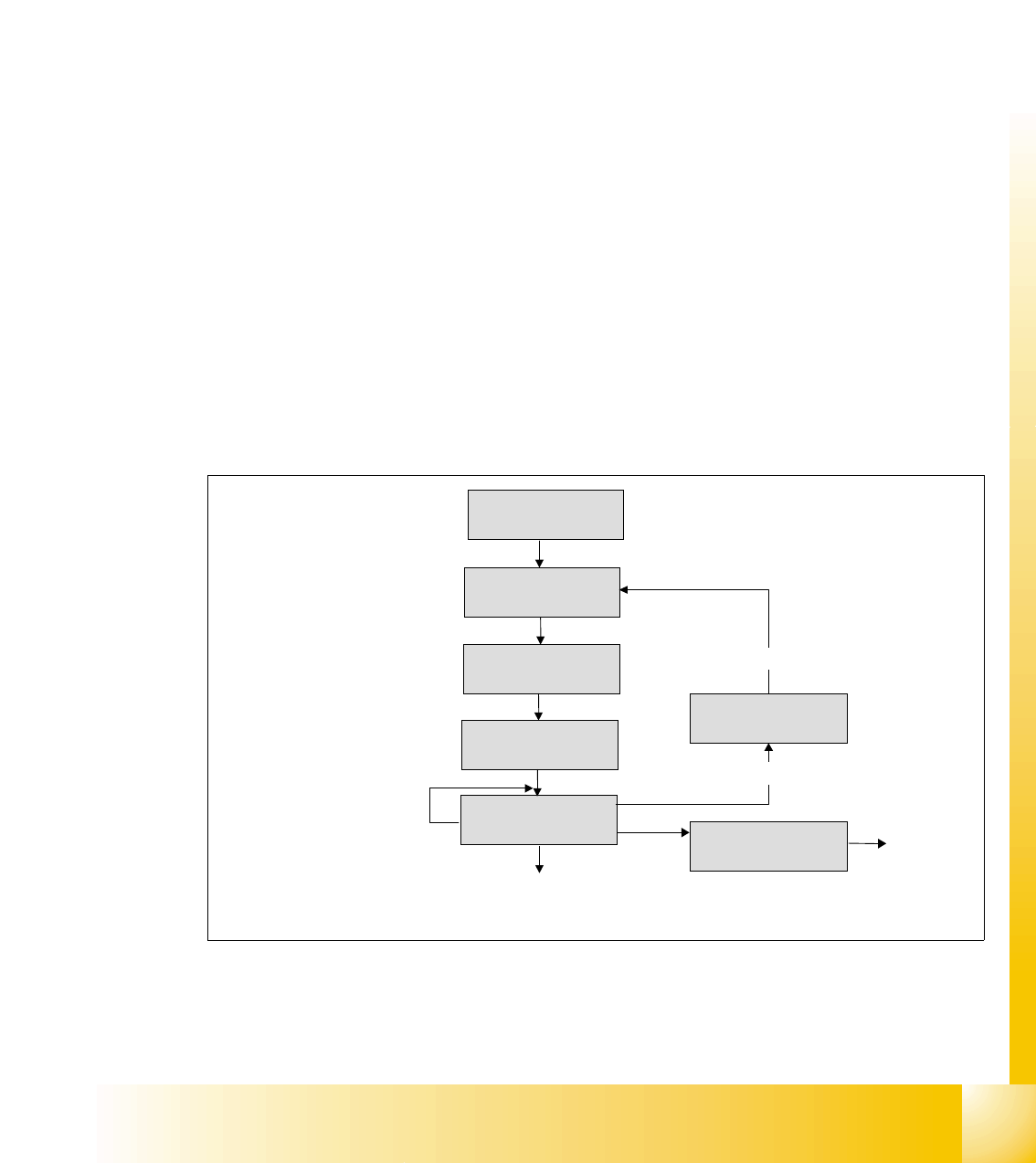

2.2.1.3 CAN Bus Arbitration

Arbitration (arbitration means decision)

In CAN networks, there is no addressing of subscribers or stations in the conventional sense, but

instead, prioritized messages are transmitted. Whenever the bus is free, any unit may start to

transmit a message. In general, a subscriber can only occupy the bus if this is free. The bus

subscriber can detect the bus occupation state by analyzing a certain time period within which the

bus must be inactive.

When multiple nodes begin to send a message at the same time, a selection phase (arbitration

phase) is used to decide which node may remain on the bus.

Bus access conflicts are resolved by including a message arbitration field (as a default the 11 bit

identifier is used).

The basis of bit-wise arbitration is the differentiation of 2 physical bus levels, a dominant one (low)

and a recessive bit (high).

A free bus is always on the recessive level. A DATA FRAME prevails over the REMOTE FRAME.

During arbitration every transmitter compares the level of the bit transmitted with the level that is

monitored on the bus. If these levels are equal the unit may continue to send.

When a recessive level is sent and a dominant level is monitored, the unit has lost arbitration and

must withdraw without sending one more bit. At the end of arbitration, the only subscriber left on

the bus is the one whose message has the lowest identifier value (logical zero is a dominant level).

The lower the identifier value is, the higher the priority of a message is.

When the bus is free any unit may start to transmit a message. The message sent by this

subscriber is not destroyed here i.e. it is a loss-free arbitration.

Fig. 2.2 - 7 flow chart bus arbitration

waiting if bus is free

bit SoF

bus in receiving state

1st bit of arbitration

transmitted

compare transmitted bit

level with bus level

bus in error state

arbitration lost?

recessive bit on dominant bus state

all arbitration bits are transmitted,

send control field and data field

next bits

START: Any member

will send a message