Q170226E01.pdf - 第320页

8.3 List of Jumper Switch Settings SERVICE MANUAL RH5 8.3−23 DA3SEC−85−540−B0 (5) Jumper setting Input jumpers for WD37C65 mode setting are as follows: Jumper Signal name Content 1o f JP12 DR V SHORT 0 16 MHZ JP12 DR V O…

RH5

8.3 List of Jumper Switch Settings

SERVICE MANUAL

8.3−22

DA3SEC−85−540−B0

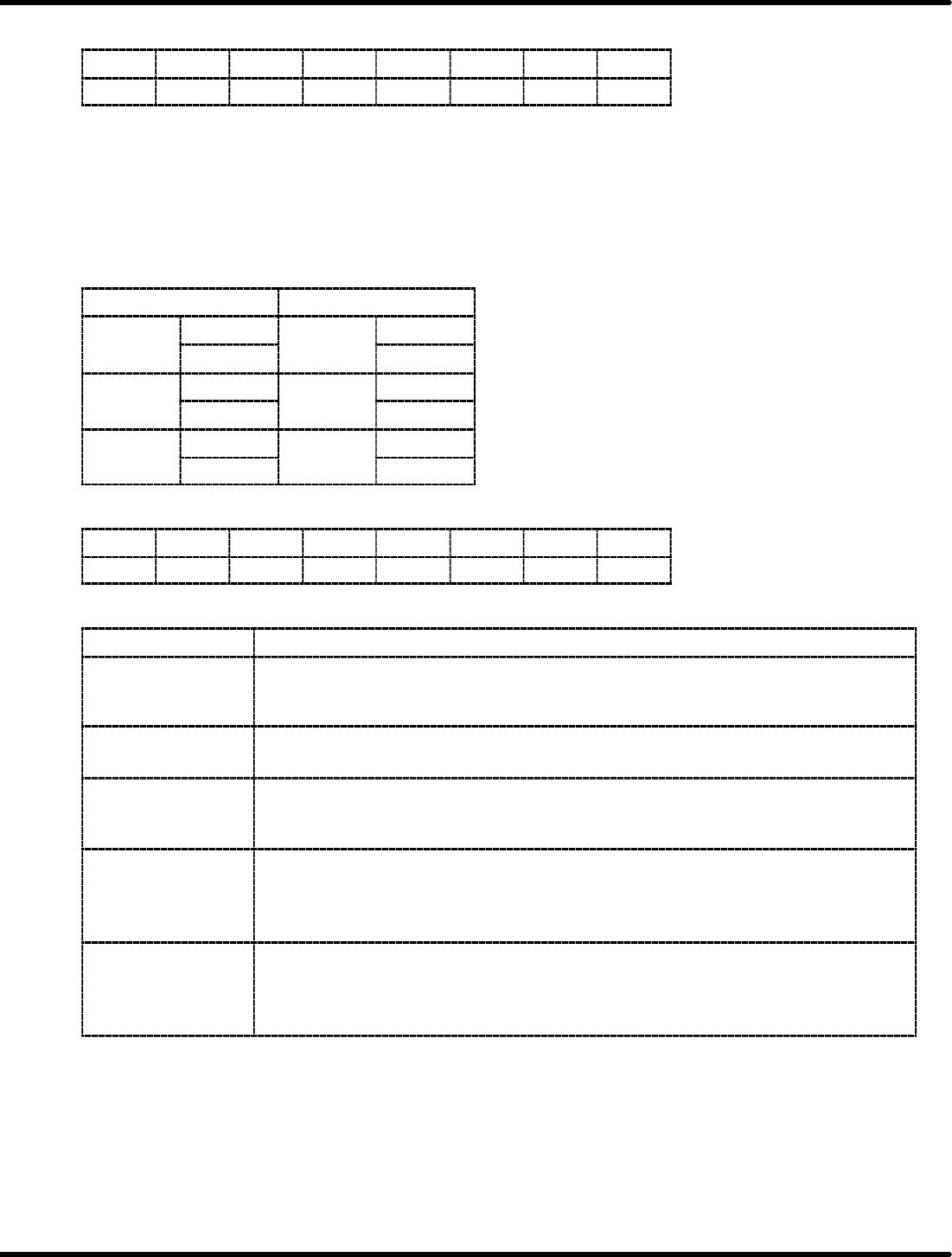

(3) Switch read

D7

D6 D5 D4 D3 D2 D1 D0

S3 S2 S1 RDY 1 1 1 1

RDY

RDY is used to check the FDD unit state by indicating external line (READY) state.

READY = “H” o RDY = “0”

READY = “L” o RDY = “1”

S1−S3

S1−S3 indicate the state at JP17 1 to 3.

JP17

S

1

OPEN

S1

1

1

SHORT

S1

0

2

OPEN

S2

1

2

SHORT

S2

0

3

OPEN

S2

1

3

SHORT

S2

0

(4) Control register

D7

D6 D5 D4 D3 D2 D1 D0

RST * * DMAE MON TMSK * TTRG

Signal Content

RST

(RESET)

Used to initialize the FDC by being changed into an input signal at the RST terminal

on the FDC (WD37C65). It can be used when the transmission is out of sequence.

This signal can be operated under POWER−ON− RESET (and SW) and also OR.

DMAE

(DMA ENABLE)

Enables the DACK signal sent from the DMA channel to transmit data. Turn ON only

when using the DMA and OFF when not.

MON

(MOTOR ON)

Controls the drive motor for the FDD unit. Operated MOTOR ON to use this signal.

MON = “0” o MOTOR ON “H”

MON = “1” o MOTOR ON “L”

TMSK

(TIMER

INTERRUPT

MASK)

This is an interrupt mask bit to mask the timer interruption of FDC (hung−up timer).

Setting this bit 0 will mask the timer interruption. Immediately after power ON, set it

to “0”. Then also set to “0” when not using the timer.

TTRG

(TIMER TRIGGER)

Triggers the hung−up timer (one−shot, triggered to approx. 100 msec).

It is used to trigger the timer for FDD motor ON/OFF controlling.

Setting both TMSK and TIRG to 0 bit will lead to the interruption approx. 100 sec

later. The timer can be re−triggered within 100 msec after the timer was triggered.

8.3 List of Jumper Switch Settings

SERVICE MANUAL

RH5

8.3−23

DA3SEC−85−540−B0

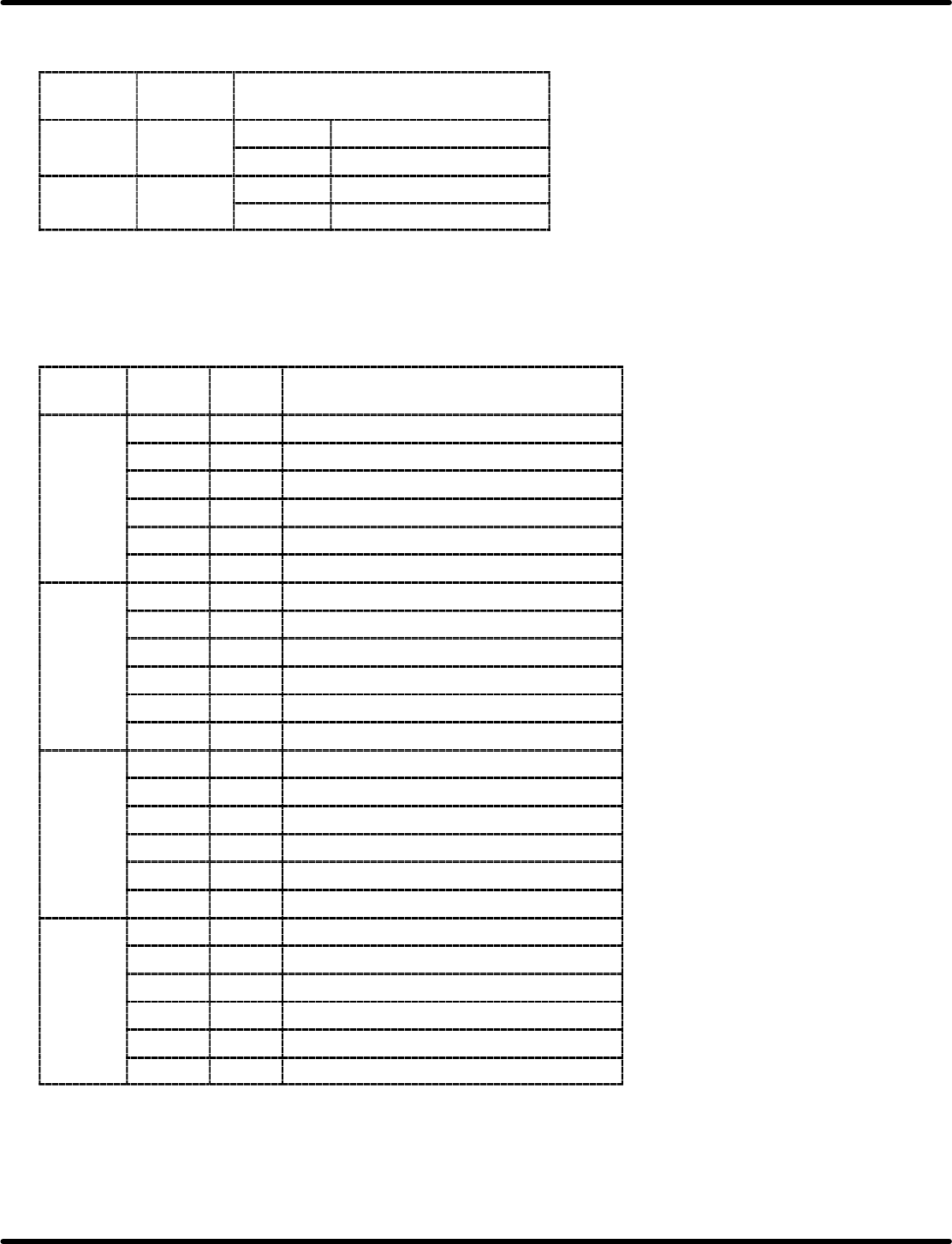

(5) Jumper setting

Input jumpers for WD37C65 mode setting are as follows:

Jumper

Signal

name

Content

1of

JP12

DR

V

SHORT 0 16 MHZ

JP12

DR

V

OPEN 1 9.6 MHz

2of

JP12

PCV

AL

SHORT 0 187 nsec

JP12

PCV

AL

OPEN 1 125 nsec

Serial interface MB89371

This board is equipped with four serial I/O interface channels. They are controlled by the two SDTRs

(Serial data transmitter receiver MB89371).

The four channels are TTY, HOST, SIO1 and SIO2. The relationship between each I/O port address and

register is given below.

Used

device

I/O

address

R/W Register

30 R Receive data buffer register

30 W Send data buffer register

TTY

32 R Status register

TTY

32 W Mode/command register

34 W Baud rate setting register

36 W Mode setting register

38 R Receive data buffer register

38 W Send data buffer register

HOST

3A R Status register

HOST

3A W Mode/command register

3C W Baud rate setting register

3E W Mode setting register

50 R Receive data buffer register

50 W Send data buffer register

SIO1

52 R Status register

SIO1

52 W Mode/command register

54 W Baud rate setting register

56 W Mode setting register

58 R Receive data buffer register

58 W Send data buffer register

SIO2

5A R Status register

SIO2

5A W Mode/command register

5C W Baud rate setting register

5E W Mode setting register

RH5

8.3 List of Jumper Switch Settings

SERVICE MANUAL

8.3−24

DA3SEC−85−540−B0

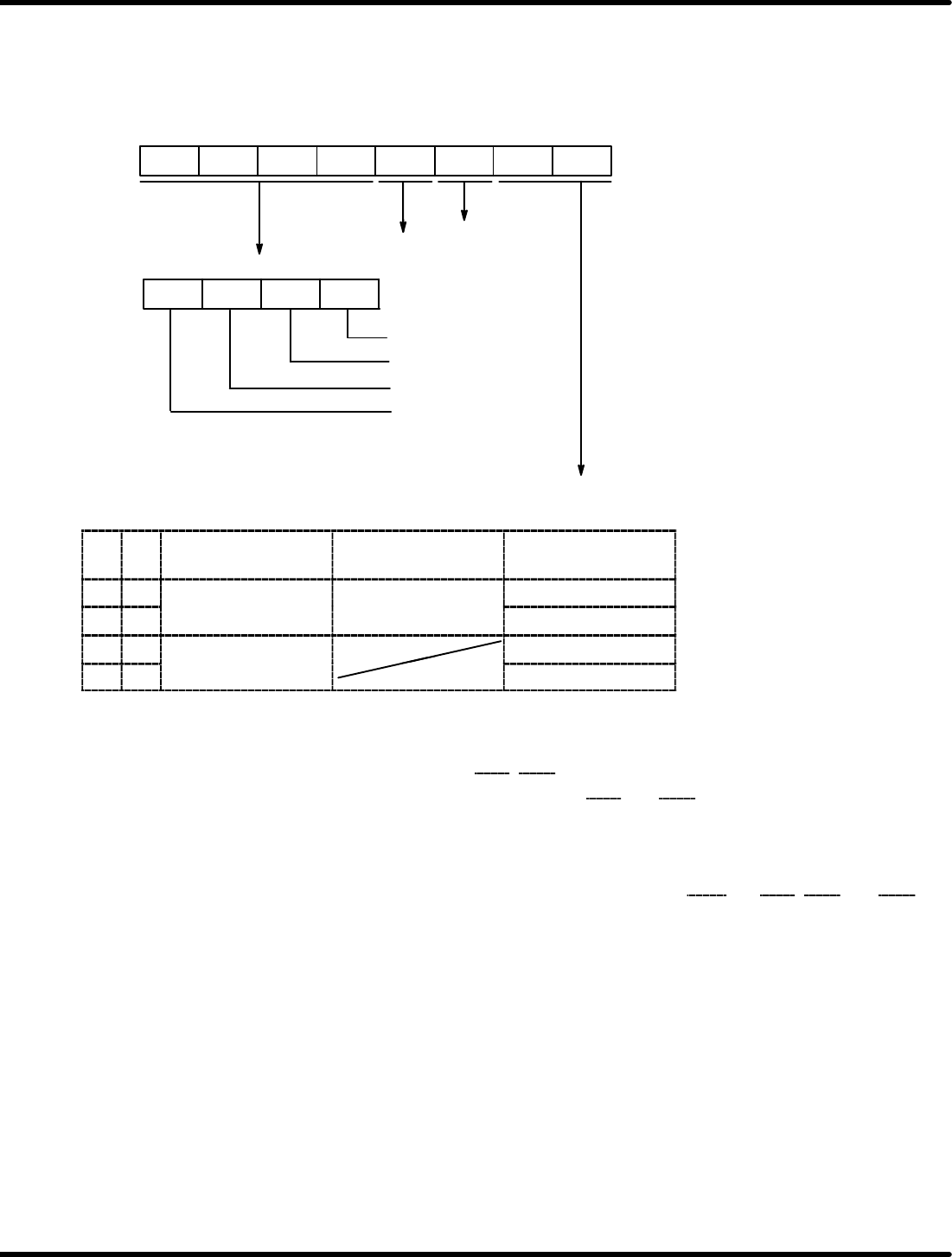

The following registers are interchangeable with the 8251A: Receive data buffer register, Send buffer

data register, Status register and Mode/command register. The mode setting register is set conforming to

the specification after resetting. Bit configuration is given below. After resetting, FO

H

is set being

interchangeable with the 8251A.

Modem control

function

Loop−back

self−check

TRNEMP mask

TRNRDY mask

RCVRDY mask

SYNDET mask

Interrupt mask bit

Clock switching

0: Mask ON (Interrupt disabled)

1: Mask OFF (Interrupt enabled)

“1” is set after resetting.

B7 B6 B5 B4 B3 B2 B1 B0

B7

B6

B5 B4

B1 B0

TRNCLK & RVCLK

of inside SDTR

TRNCLK & RVCLK

of MB89371

TRNEMP, ST1

0 0 Sent from external

lk

Input

TRNEMP

0 1

clock

I

npu

t

ST1

1 0 Uses internal baud

t

t

TRNEMP

1 1

rate generator.

ST1

=REFERENCE=

Modem control function

x Set the level of the modern control line CTS

, DSR by setting either “0” or “1” at B2.

x When “1” is set for B2, the “L” level is set at terminals CTS

and DSR.

x When set to “0” for B2, the normal operation mode is set.

=REFERENCE=

Loop−back self−check

x In the loop−back self−check mode, terminals TRNDT and RCVDT, RTS

and CTS, DTR and DSR

are connected each other inside the MB89371. Transmission, reception and checks are performed

entirely by the MB89371.

Set 1 at B3 to engage this mode.

Set 0 at B3 to engage normal operation mode.