Q170226E01.pdf - 第327页

RH5 8.3 List of Jumper Switch Settings SERVICE MANUAL 8.3−30 DA3SEC−85−540−B0 Bus interrupt From this board, it is possible to notify another board of the interrupt and input a notification from another board as the inte…

8.3 List of Jumper Switch Settings

SERVICE MANUAL

RH5

8.3−29

DA3SEC−85−540−B0

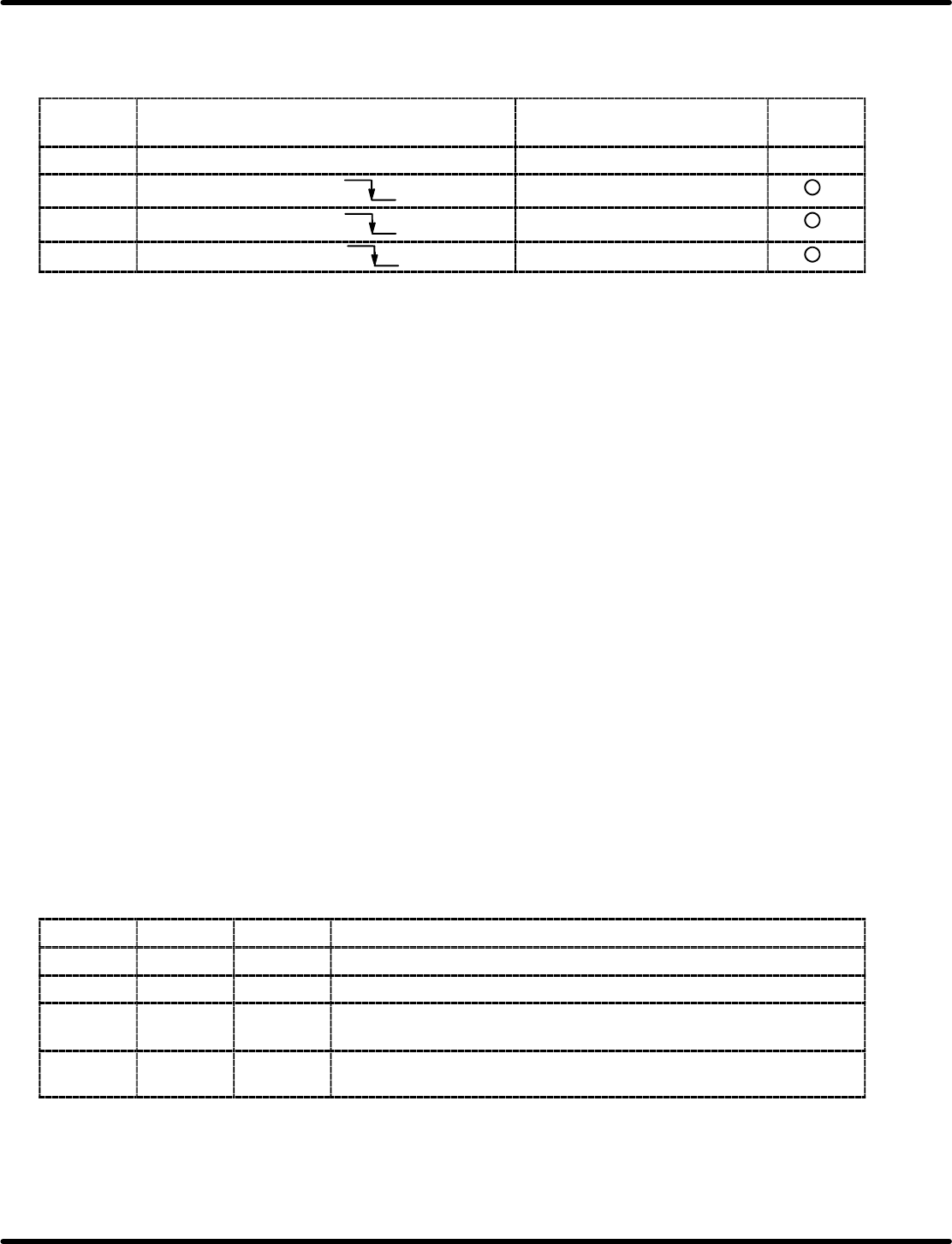

NMI and RESET

From this board, it is possible to notify the NMI (CPU) of the four factors making up the non−maskable

interrupt. Furthermore, factors can be confirmed using mask control and status data.

NMI

factor

Source address Status data Mask

ON/OFF

SW Push SW SW2 on board front D3 bit from port 22 H u

PFIN P2 bus A28 D2 bit from port 22 H

WDT P2 bus C28 D1 bit from port 22 H

ERROR 8 for JP11 D0 bit from port 22 H

This board is initialized with the following signals.

1. Reset circuit at power ON

Using the MB3771, a reset pulse can be transmitted approximately 100 msec when

power is ON or a voltage drop down to approx. 4.3V.

2. Push SW (Board front SW1)

Using the MB3771, a reset pulse can be transmitted for about 100 msec when SW1 is

pressed or after having been pressed..

3. PR bus INIT * (A6)

4. P2 bus RESET * (C27)

While INIT * and RESET * on the P2 bus line are set to “L”, the reset state is ON.

Bus interface setting

(1) BCLK: JP4

Short: BCLK (9.8304 MHz) is output to B6 of P2.

Open: BCLK is not output. (Output comes from another master instead.)

(2) CCLK: JP3

Short: CCLK (9.8304 MHz) is output to A12 of P2.

Open: CCLK is not output. (Other master will be output.)

(3) BPRO: JP10

Short: BPRO is output to C6 of P2.

Open: BPRO is not output.

(4) Bus release: JP9

JP9

CBRQ ALWAYS Description

B−C HorL L Bus is released at the end of every bus cycle.

Open L H Bus is released at the end of every bus cycle regardless of priority.

Open H H

Bus is not released until either CBRQ= “L” changes into BPRN= “H”

or the CPU is assumed to a halt.

A−C

HorL Connected

to reset

Bus is not released until either the bus master priority changes to

BPRN= “H” or the CPU is assumed to a halt.

RH5

8.3 List of Jumper Switch Settings

SERVICE MANUAL

8.3−30

DA3SEC−85−540−B0

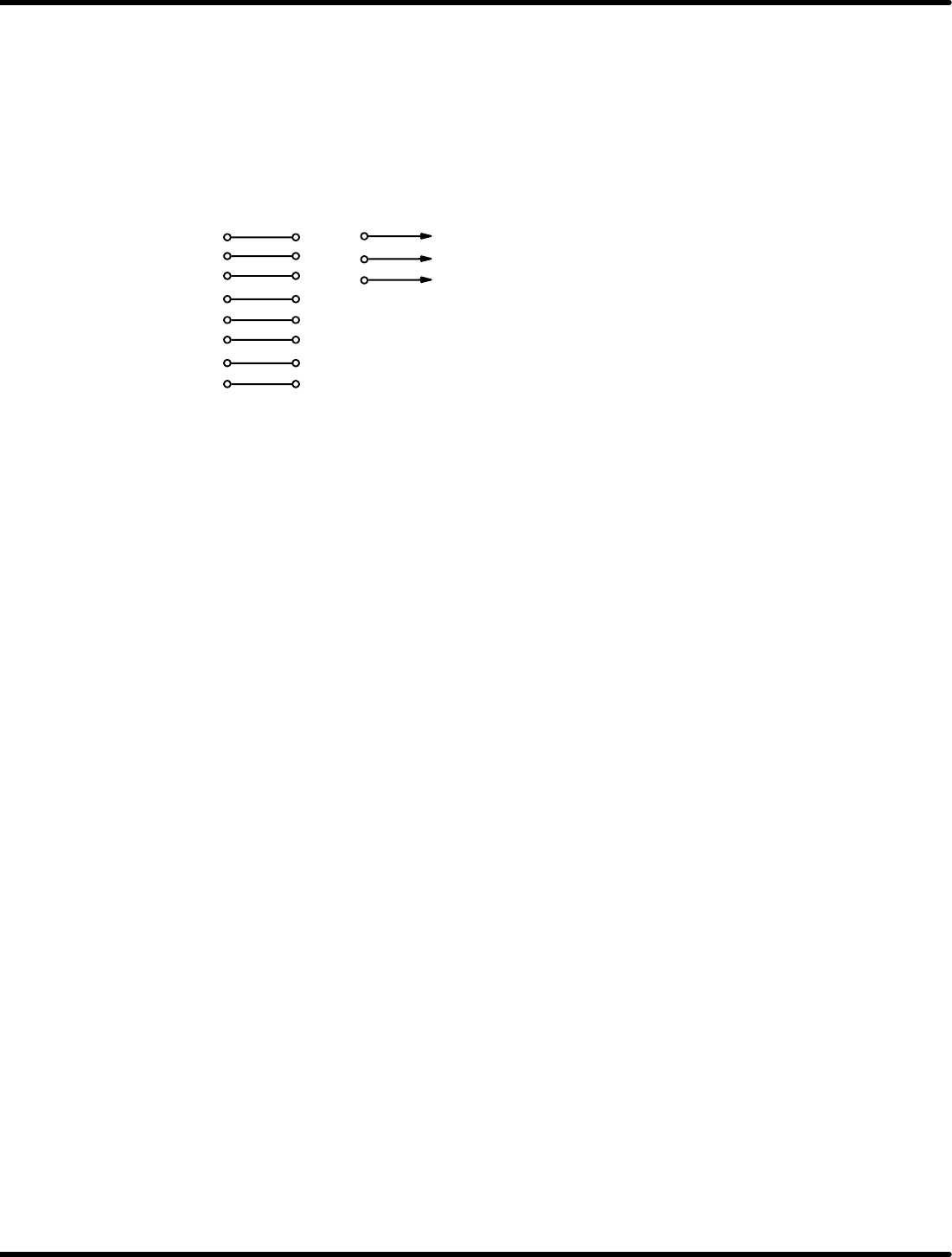

Bus interrupt

From this board, it is possible to notify another board of the interrupt and input a notification from another

board as the interrupt, by going through the P2 bus interrupt notification line (line 8 of INT0−INT7).

Furthermore, a dual port interrupt can be done by writing into the specified memory area on this board.

(1) Interrupt notification line and setting

The P2 is connected to interrupt notification line with JP11.

P2 bus

JP11

INT7 A13

INT6 B13

INT5 C13

INT4 A14

INT3 B14

INT2 C14

INT1 A15

INT0 B15

ERROR

IR3 (Command interrupt)

DENT notification

7

6

5

4

3

2

1

0

8

9

10

(2) Command interrupt

A notification from another board can be notified as the interrupt by connecting 0−7 with 9 of JP11.

The interrupt is notified to level 3 of the master 8259A.

(3) Dual port interrupt

Writing the optional data into the last four bytes (FFFC

H

to FFFF

H

) in the segment (64 K) setting with

SW12 as explained in dual port RAM enables the interrupt to notify to level 5 of the master 8259A.

8.3 List of Jumper Switch Settings

SERVICE MANUAL

RH5

8.3−31

DA3SEC−85−540−B0

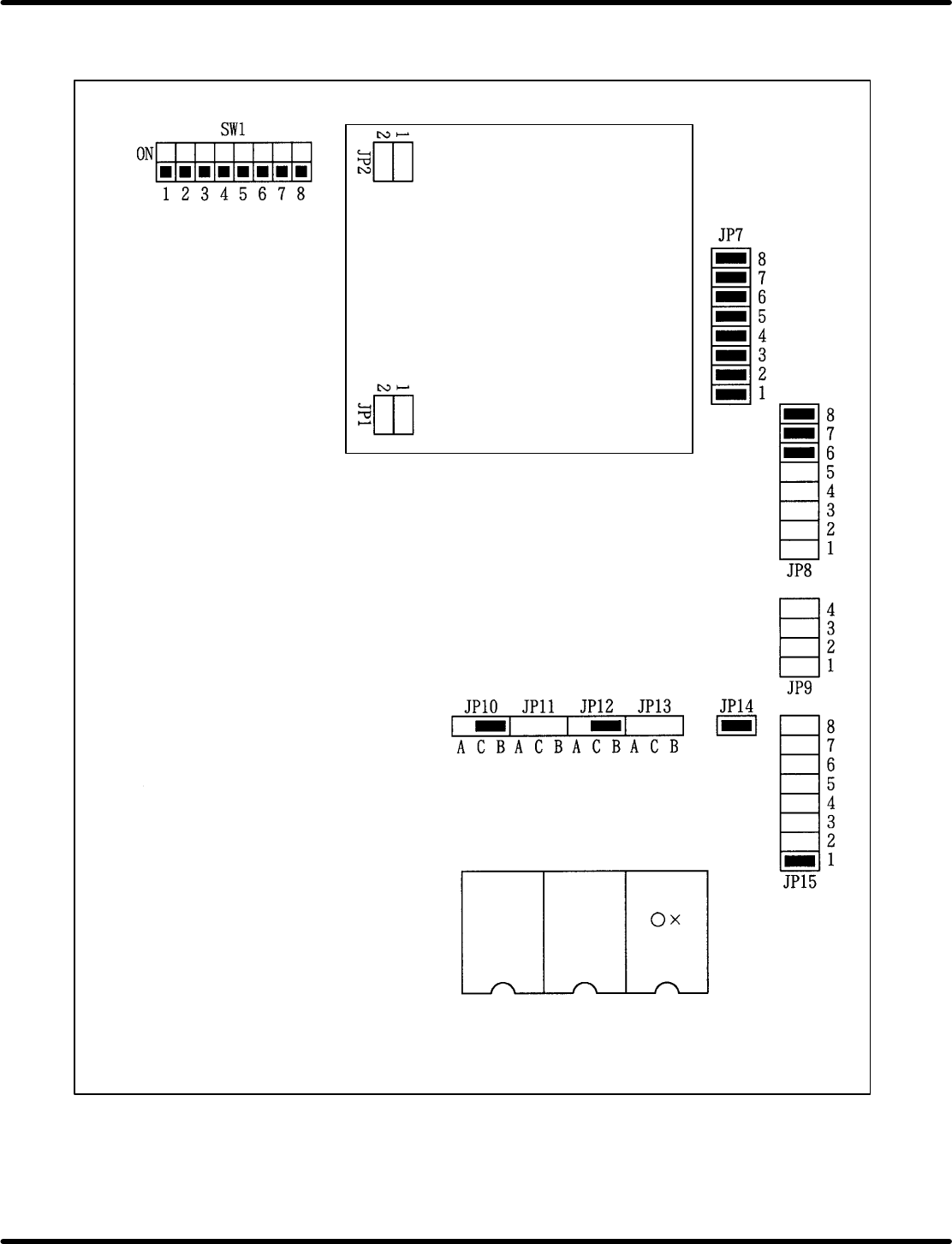

8.3.5 SEQ−SE (I) Board Setting

DST−S board

Firmware

H

Firmware

L