Q170226E01.pdf - 第331页

RH5 8.3 List of Jumper Switch Settings SERVICE MANUAL 8.3−34 DA3SEC−85−540−B0 8.3.6 APC Board Setting SW1: Reset SW SW2: For interrupt setting SW3: Address setting on the multibus in dual port RAM. SW4:

8.3 List of Jumper Switch Settings

SERVICE MANUAL

RH5

8.3−33

DA3SEC−85−540−B0

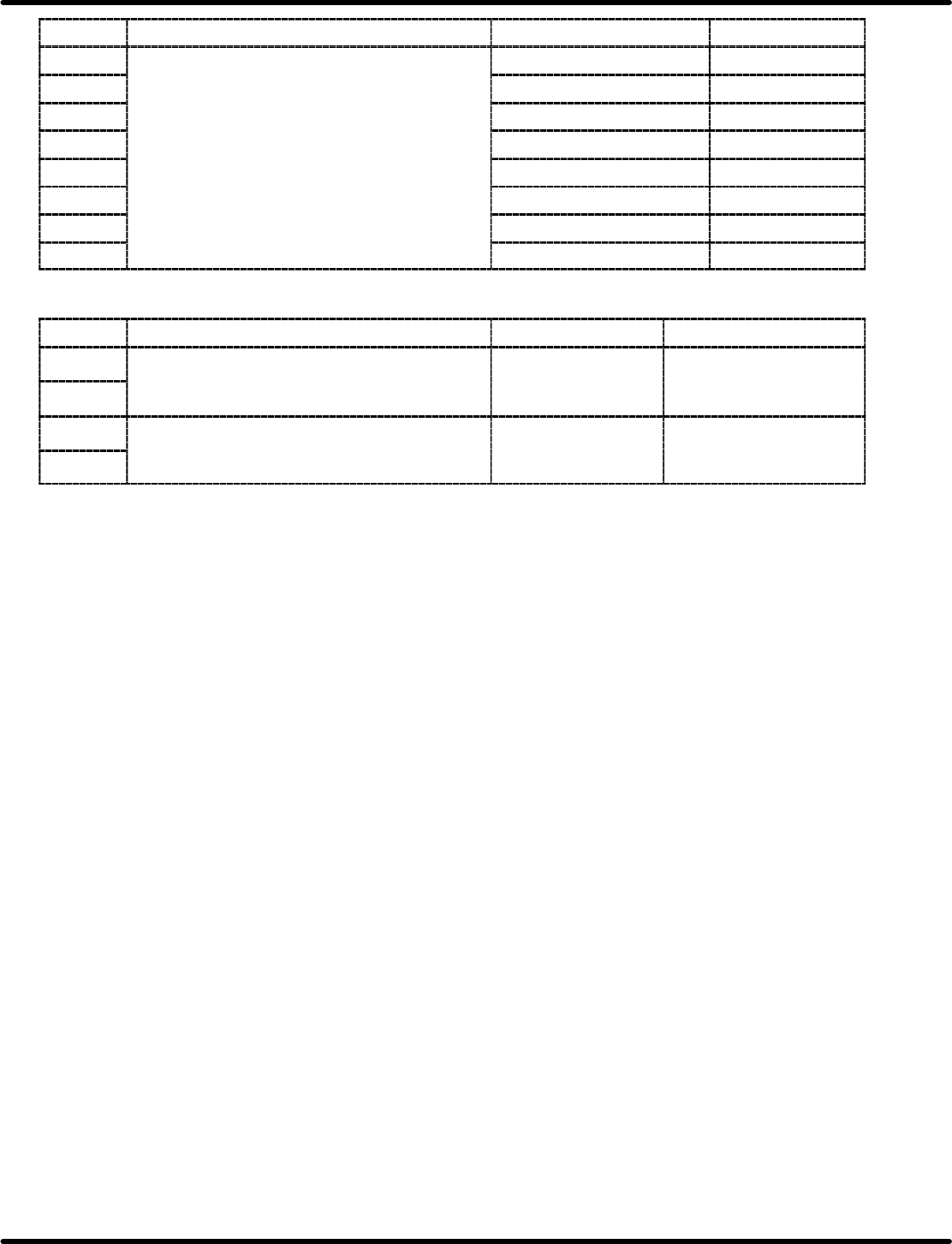

JP name Description Short or A−C Open or B−C

JP15−1 Output level setting for multibus interrupt

(MEND)

Output to MINT0 * *1 Not used

JP15−2

(MEND)

Output to MINT1 * Not used

JP15−3 Output to MINT2 * Not used

JP15−4 Output to MINT3 * Not used

JP15−5 Output to MINT4 * Not used

JP15−6 Output to MINT5 * Not used

JP15−7 Output to MINT6 * Not used

JP15−8 Output to MINT7 * Not used

DST−S (I) expansion board

JP name Description Short or A−C Open or B−C

JP1−1 Rotary encoder power supply selection Select 1 and 2 to

use

internal

power

Select 1 and 2 to use

external

power

supply

JP1−2

+12V

use

i

n

t

erna

l

power

supply.

ex

t

erna

l

power supp

l

y.

*1

JP2−1 Rotary encoder power supply selection Select 1 and 2 to

use

internal

power

Select 1 and 2 to use

external

power

supply

JP2−2 COMMON

use

i

n

t

erna

l

power

supply.

ex

t

erna

l

power supp

l

y.

*1

Columns marked with *1 indicate standard factory setting.

RH5

8.3 List of Jumper Switch Settings

SERVICE MANUAL

8.3−34

DA3SEC−85−540−B0

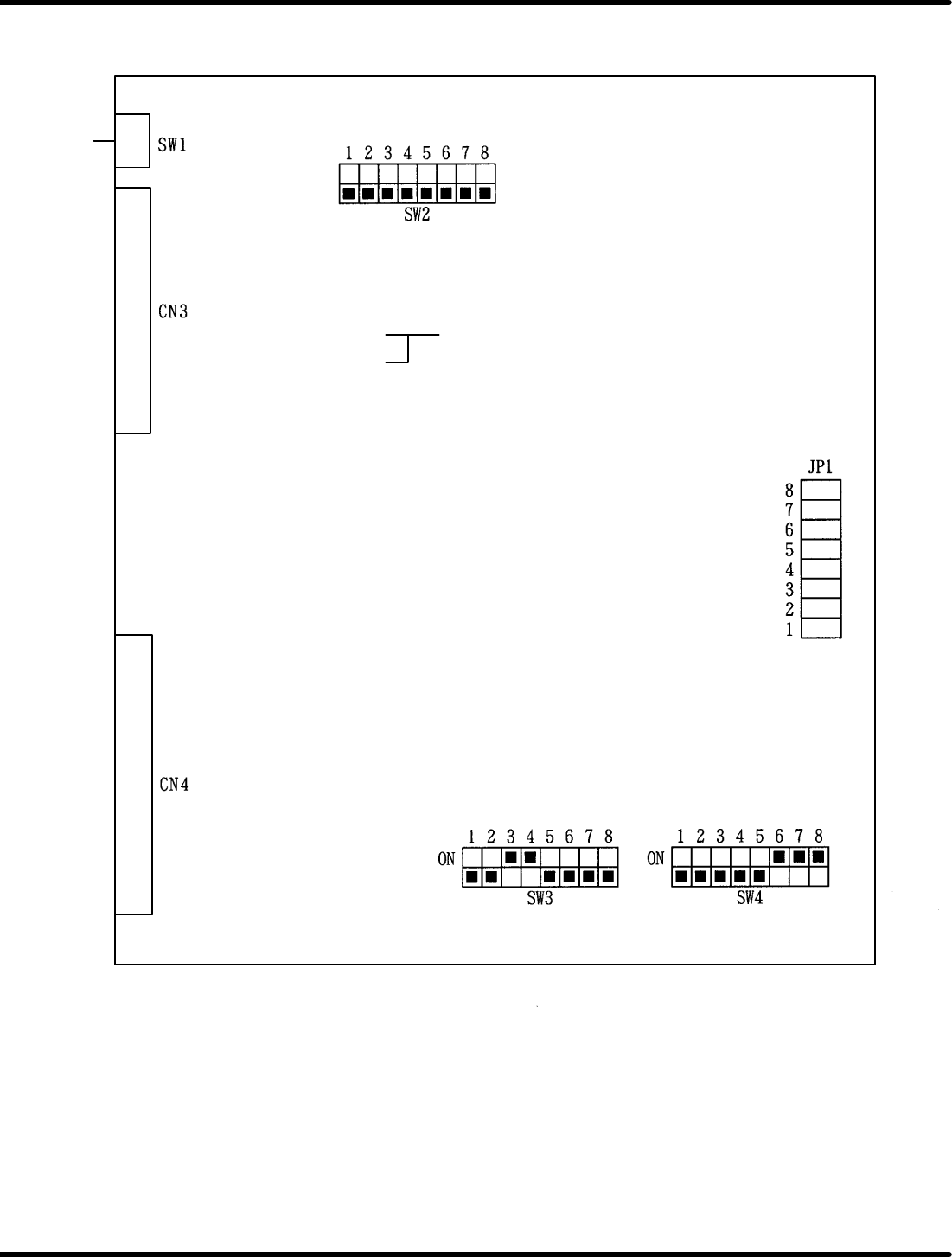

8.3.6 APC Board Setting

SW1: Reset SW

SW2: For interrupt setting

SW3: Address setting on the multibus in dual port RAM.

SW4:

8.3 List of Jumper Switch Settings

SERVICE MANUAL

RH5

8.3−35

DA3SEC−85−540−B0

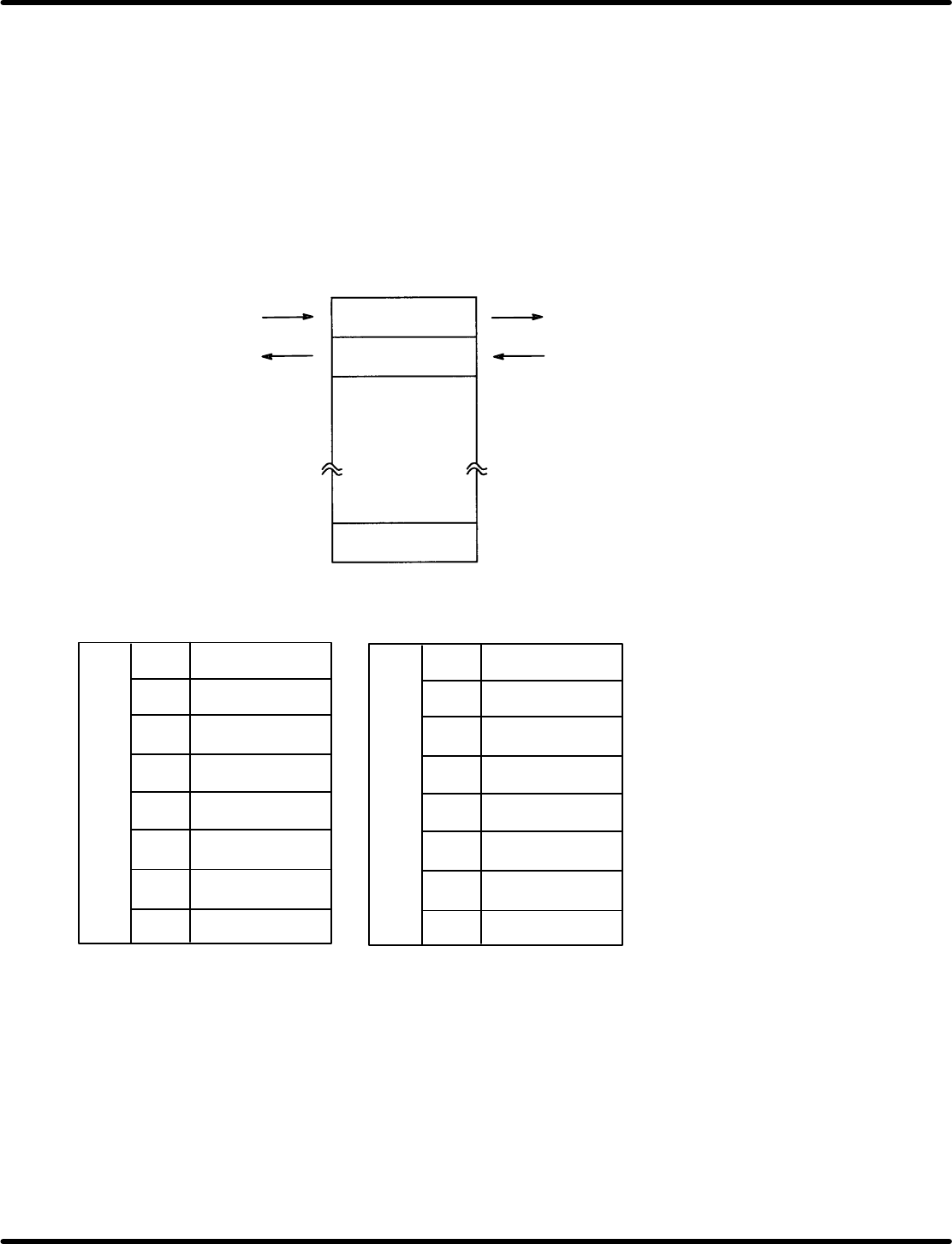

Multibus interface

(1) Dual port RAM

This board cannot directly access to the multibus. (slave mode only).

Communications with the main CPU can be done passing through the dual port RAM on this board. It

is possible to send the interrupt notification to the main CPU through the multibus interrupt line, by

writing the interrupt into the 7FE address (offset address) from the MPU (64180) on this board.

This factor will be released by reading−out the same address on the main CPU.

Similarly, the interrupt will be notified through INT0 of the MPU on this board, by writing the interrupt

into the 7FF address from CPU. This factor will be released by reading−out the same address on the

internal MPU.

Always bite−access to the host CPU.

For details, see the MB8421 manual.

Host CPU side

Internal CPU side

7FFH

7FEH

000H

The address map seen from the host CPU is set with DIP SW3 and SW4 on the board.

SW3

ON: 1

OFF: 0

ADRF

1

2

3

4

5

6

7

8

ADRE

ADRD

ADRC

ADRB

Not used

Not used

Not used

SW4

ADR23

1

2

3

4

5

6

7

8

ADR22

ADR21

ADR20

AD13

AD12

AD11

AD10